Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

(1 т

О "бА -ЙИ Е

ИЗОБРЕТЕНИЯ ii) 467409

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 18.07.73 (21) 1945054/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.04.75. Бюллетень № 14

Дата опубликования описания 20.08.75 (51) М. Кл. G 11c 29/00

Государственны к комитет

Совета Министров СССР по делам изобретений (53) УДК 681.327.6 (088.8) и открытий (72) Авторы изобретения

Е. П. Балашов, В. А. Доронин, А. П. Жмакин, А. О. Тимофеев и Л. А. Шумилов

Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство с автономным контролем, содержащее накопитель, входы которого подключены к дешифратору адреса и формирователям записи, а выходы— к усилителям считывания, схему свертки по модулю три, вход которой соединен с выходом регистра адреса, а выход — с одним входом первой схемы сравнения, схему свертки по модулю два, вход которой подключен к регистру числа, а выход — ко второй схеме сравнения, и схему «ИЛИ», одни входы которой соединены с выходами схем сравнения. Накопитель известного устройства содержит три контрольных разряда, В первый контрольный разряд записывается дополнение до нечетности кода информационных разрядов записываемого числа,,в два оставшихся контрольных разряда — остаток от деления кода адреса ячейки на три. После считывания слова из накопителя первый контрольный разряд сравнивается с выходом схемы свертки содержимого регистра числа по модулю три. Это сравнение дает возможность обнаружить одиночные ошибки при считывании числа из накопителя. Два других контрольных разряда сравниваются с выходом схемы свертки содержимого регистра адреса по модулю три, что дает возможность выявлять считывание по ложному адресу.

К недостаткам известного устройства относится то, что оно примерно в 15% случаев не может обнаружить такие распространенные в запоминающем устройстве сбои, как срабатывание двух (реже нескольких) адресных шин (сбой типа «раздвоение тока») или полное несрабатывание адресного тракта («обрыв»).

В первом случае с большой степенью вероятности в контрольных разрядах появляется

10 комбинация 111, а во втором — комбинация

000. Однако эти же комбинации могут появляться в контрольных разрядах и при правильном считывании информации из накопителя. Следовательно, некоторые сбои типа «раз15 двоение тока» или «обрыв» не могут быть обн ар уж ен ы.

Описываемое устройство отличается от известного тем, что оно содержит схемы форми20 рования обратного кода и дополнительный дешифратор, входы которого подключены к контрольным разрядам регистра числа, а выходы — к другим входам схемы «ИЛИ». Входы первой схемы формирования обратного кода

25 соединены с выходами схем сверток по модулю два и три, а .выход — с формирователями записи контрольных разрядов. Входы второй схемы формирования обратного кода подключены к контрольным разрядам регистра числа, 30 а выход — к другому входу первой схемы сравнения.

467409

Остаток от деления кода адреса на три

Коды контрольных разрядов

Дополнение до нечетности числа

Указанные отличия позволяют повысить надежность устройства.

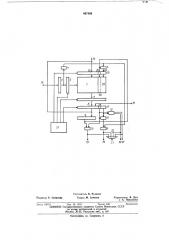

На чертеже изображена блок-схема запоминающего устройства.

Устройство содержит накопитель 1, регистр

2 адреса, дешифратор адреса 3, схему свертки по модулю три 4, первую схему 5 формирования обратного кода, первую схему 6 сравнения, усилители считывания 7, регистр 8 числа, схему 9 свертки по модулю два, вторую схему 10 сравнения, вторую схему 11 формирования обратного кода, дешифратор 12 и формирователи записи 13, связанные с кодовыми шинами числа 14. Регистр 8 подключен к шинам 15, а регистр 2 — к шинам 16. Устройство содержит также блок управления 17.

Выходы 18 и 19 схем 10 и 6, а также выходы

20 и 21 дешифратора 12 соединены со входами схемы «ИЛИ» 22, имеющей выход 23.

Выходы схем 4 и 9 подключены ко входам схемы 5, выход 24 которой соединен с формирователями записи:«.îíòðîëüíûõ разрядов 25.

Один из входов схемы 5 связан с рормирователем записи контрольного разряда 26. Входы дешифратора 12 подключены к контрольным разрядам 27 и 28 регистра 8. Входы схемы 11 соединены с разрядами 27 и 28 регистра 8, а выход — со входом схемы 6. Накопитель имеет контрольные разряды 29 и 30.

Кодирование информации в запоминающем устройстве осуществляется таким образом, что комбинации 000 и 111 являются запрещенными и их появление свидетельствует о соответствующих типах сбоев. Принята следующая кодировка контрольных разрядов, показанная в таблице.

Остаток по модулю три представлен в двоичном коде «с избытком 1». Разряд нечетности интерпретируется, как знаковый. Если он равен 1, то остаток по модулю три записывается в обратном коде.

Запоминающее устройство работает следующим образом.

При записи информации в накопитель 1 в контрольный разряд 30 заносится признак, до5

60 полняющий число единиц в информационных разрядах числа до нечетного. В разряды 29 заносится значение остатка от деления содержимого регистра 2 адреса на три в прямом или обратном коде «с избытком 1» (согласно таблице). Значение разряда 30 формируется схемой 9 свертки по модулю два. Остаток от деления содержимого регистра адреса на три формируется схемой 4 свертки в прямом коде

«с избытком 1». Схема 5 при необходимости инвертирует код остатка.

После считывания информации из накопителя 1 на регистр 8 числа происходит сравнение па схеме 10 сравнения контрольного разряда остатка числа по модулю два, хранящегося в разряде 28 регистра 8 числа, и выходе схемы

9 свертки по модулю два. В случае неравенства входных сигналов схема 10 формирует на своем выходе 18 сигнал «ложная информация». На схеме 6 сравнения сравниваются остатки по модулю три от кода адреса ячейки.

На один вход схемы 6 поступает код остатка со схемы 4, а на другой вход — со схемы 11 формирования обратного кода. В случае несовпадения кодов на входах схемы 6 сравнения, на ее выходе 19 появляется сигнал «ложный адрес». Дешифратор 12 выделяет в контрольных разрядах комбинации 000 и 111 и формирует па выходе 20 сигнал «раздвоение тока», а на выходе 21 — сигнал «обрыв». Схема «ИЛИ» 22 формирует на своем выходе 23 общий сигнал «ошибка».

Предмет изобретения

Запоминающее устройство с автономным контролем, содержащее накопитель, входы которого подключены к дешифратору адреса и формирователям записи, а выходы — к усилителям считывания, схему свертки по модулю три, вход которой соединен с выходом регистра адреса, а выход — с одним входом первой схемы сравнения, схему свертки по модулю два,,вход которой подключен к регистру числа, а выход — ко второй схеме сравнения, и схему «ИЛИ», одни входы которой соединены с выходами схем сравнения, о т л и ч а ю щ е ее я тем, что, с целью повышения надежности устройства, оно содержит схемы формирования обратного кода и дополнительный дешифратор, входы которого подключены к контрольным разрядам регистра числа, а выходы — к другим входам схемы «ИЛИ», входы первой схемы формирования обратного кода соединены с выходами схем сверток по модулю .два и три, а выход — с формирователями записи контрольных разрядов, входы второй схемы формирования обратного кода подключены к контрольным разрядам регистра числа, а выход — к другому входу первой схемы сравнения.

467409

19 ", 2021

Составитель В. Рудаков

Техред М. Семенов

Корректоры: В. Дод и А. Николаева

Редактор Е. Семанова

Типография, пр. Сапунова, 2

Заказ 1997/2 Изд. № 1464 Тираж 648 Подписное

UHHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5