Устройство для преобразования случайной последовательности импульсов в коррелированные сигналы

Иллюстрации

Показать всеРеферат

Бср1-о!овнами

О П И (. А-Н*

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«1467454 (6! ) Дополпптел! ное к авт. сгIIд-ву— (22) Заявлено 18.01.73 (21) 1881300/26-9 (5l) М. Кл. H 031< 5/156 с IIpIIcnc II;!cIII!eiI заявки ¹ ——

Государственный квинтет

Свввта Мнниетрав СССР вв делам изебретений и открытий (23) Приоритет—

Опубликовано 15.04.75. Б!оллетевь ¹ 14

Дата опубликования описания 28.11.75 (э3) УД К 621.376.6 (088.8) (72) Авторы изобретения

В. М. Масловский и A. Д. Гуменюк (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ СЛУЧАЙНОЙ

ПОСЛ ЕДОВАТЕЛ Ь НОСТИ ИМП УЛ ЬСО В

В КОРРЕЛИРОВАННЫЕ СИ ГНАЛЫ

Устройство от нос!!гся к технике передачи дагтиых и может быть использовано для скоростной передачи дп<п<ретиых сигналов по каналам связи.

Известно устройство для преобразования случайиои последовательности импульсов в коррелцрова1гпые II! IIaлы, содержащее синхронизатор, подкл!оче1!пый к первым входам блоков памят I, сумматор, к в«одам которого

11одк, !1очец!! экстраполяторы.

Однако,известное устройство имеет недостаточную скорость передачи сигналов по каналам связи.

С целью повышения удельной скорости передачи дискретной информации по каналам связи с ограниченной полосой частот в предлагаемое устройство дополнительно введены клапаны, формирователь непрерывного коррелированного сигнала и узел управления, при этом выход сумматора подключен к входу формирователя непрерывного коррелироваииого сигнала и к одному из блоков памяти, соединенных последовательно между собой через клапаны, к другим входам последних подключен другой выход синхронизатора, а выходы клапанов подключены к входам соответствующих экстраполяторов, причем к третьим входам блоков памяти подключен выход узла управления, соединенного с синхронизатором; кроме того, формирователь непрерывного коррелироваиного сигнала содержит формирователь напряжения подставки, выход которого одновременно подключен к первым входам блоков вычисления и суммирования, и датчик случайных последовательностей, выход которого подключен к другим входам блоков вычитаиия и суммирования.

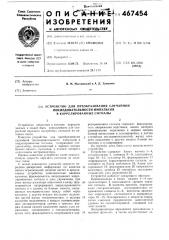

11а чертеже дана блок-схема предлагаемого устройства.

10 Устройство содержит блоки памяти 1 — 4, IIII«po1I1!aaxop 5, клапаны 6 — 9, электрополяторы 10 — 15, сумматор 16, формирователь 17 псп!рерывиого корретироваиного сигнала, состоящего пз блока вычитания 18, блока сум15 мпроваипя 19, формирователя 20 напряжения подставки, датчика 21 случайны«последовательностей, узел уира вле!!пя 22.

Устройство работает следующим образом.

Первоначально в блоки памяти 1 — 4 спн20 «ронпзатором 5 записывается среднее зиаче1гпе cIII.IIaла. В моменты !врех!ецп, определяемые синхронизатором, последовательно открываются клапаны 6 — 9, величп1!ы записанпы«напряжений считываются в эксграполя25 торы !О- — 15. Одновременно в моменты открывания клапанов продвигается запомиепиы!! уровень иа соответствующий следящий элемент памяти.

Экстраполяторы определяют производные и

30 весовь1е фуикц11п, а T3I

21 случайных чисел напряжения. На выходе 23 образуются непрерывные коррелированные сигналы,.поступающие в канал связи и на вход:блока памяти 1.

Узел управления 22 предназначен для стирания элементов памяти и управляется синхронизатором, который получает сигнал от этого узла о записи иоходной комбинации через интервалы времени, определяемые допустимым значением накопленной ошибки.

Таким образом, устраняется эффект накопления ошибок эстраполяции, свойственный систем е коррел иров а ния сигналов.

П р е д м е т и з об р е т е н и я

1. Устройство для преобразования случайной последовательности импульсов,в коррели4 рованные сигналы, содержащее синхронизатор, подключенный к первым входам блоков памяти, сумматор, к входам которого подключены экстраполяторы, отличающийся тем, что, с целью повышения удельной скорости передачи дискретной информации по каналам связи с ограниченной полосой частот, в устройство дополнительно введены, клапаны, формирователь непрерывного коррелированного сигнала и узел управления, прп этом выход сумматора подключен к входу формирователя непрерывного коррелированного сигнала и к одному из блоков памяти, соединенных последователыно между собой через клапаны, к дру15 гим входам последних подключен другой выход GHIHxðîíèçàòîðà, а выходы клапанов подключены .к входагм соответствующих экстраполяторав, причем к третьим входам блоков памяти подключен выход узла управления, со20 едипенного с синхронизатором.

2. Устройство по п. 1, отличающееся тем, что формирователь непрерывного коррелп рова нного сигнала содержит формирователь на25 пряжения подставки, выход которого одновременно подключен к,первым входам блоков вычитания и суммирования, и датчик случайных последовательностей, выход которого подключен к другим входам блоков вычитания и сум30 мировання.