Накопитель-счетчик

Иллюстрации

Показать всеРеферат

О П И С Н И Е 467477

Со-са Советских

Сс цмлистических

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (Gl1 Дополнительное к авт. свид-ву —— (22) Заявлено 4.08.73 (21) !956486. 26-9 (52) М. Кл. Н 03k 25/00

Н 04/ 13/08 с присоединением заявки №вЂ”

Гасударствеииый комитет

Соната Министров СССР по делам изоаретеиий и аткрыти" (32) Приоритет ——

Опубликоват1о 15,04.75. Бюллетень ¹ 14 (53) УД К 68 .3.055 (088,8) Дата опубликования описания 11.05.76 (72) Автор изобретения

П. А. Сосин (71) Заявитель (54) НАКОПИТЕЛЬ-СЧЕТЧИК

Изобретение относится к области телеграфии и передачи данных и может быть испо,1ьзовано в оконечных устройствах.

Известен накопитель-счетчик, содержащий матрицу элементов памяти, устройство управления накопителем, соединенное с коммута ором тактов, и исполнительное устройство, соединенное со входом управления, приемо"r, причем в столбце выход каждого элемента!гамяти соединен со входом последующего элемента памяти, входы элементов памяти ка>идой строки соединены с выходами коммугатi)ра тактов, входы элементов памяти первой строки соединены с шинами входных сигналов.

С целью упрощения устройства в нем вы: од элемента памяти каждого столбца последней строки соединен с первым дополнительным входом элемента памяти первой строки следующего столбца, выход элемента памяти последнего столбца последней строки соединен с первым входом дополнительного полусумматора, второй вход которого соединен с выходом одного из элементов памяти, выход пол;сумматора соединен через вновь введенный ннвертор с первым входом дополнительного вентиля, .второй вход которого соединен со входом управления приемом, а выход — с первым дополнительным входом элемента памяти первой строки первого столбца, вторые дополнительные входы элементов памяти первой строки соединены с дополнительным выходом коммутатора тактов, выходы всех элементов памяти соединены со в:одами вновь введенного дешнфратора, выход которого соединен со входом

1сполнительного устройства.

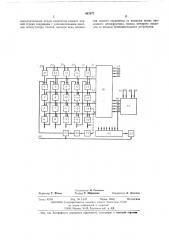

На чертеже приведена блок-схема предлагаемого накопителя-счетчика.

1!акоп итель-счетчик содержит элеме!ггьт тр 1 — 20 (триггера) памяти, входные схемы «И»

21 — 25, шины 26 — 30 входных сигналов, тактовые шипы 31 — -35, коммутатор 36 тактов, тактовые шины 37 — 40, устройство 41 управления накопителем, вход 42 с приемника, вход 43 с !

5 печатающего устройства, выход 44 устройства управления накопителем, дешифратор 45, шины 46 — 49 сигналов управления, тактовые шины 50 — 51, исполнительное устройство 52, полусумматор 53 по модулю 2, инвертор 54, схе2р му «И» 55 и вход с приемника 56.

Накопитель-счетчик состоит из элементов

1 — 20 памяти, расположенных мат рицей с и строками (ступенями) и т столбцами. Выход каждого элемента столбца соединен со входом

25 последующего. Входы элементов первой ступени соединены с.выходами элементов последней ступени и через схемы «И» 21 — 25 — с входными шинами 26 — 30.

Вторые входы схем «И» 21 — 25 соединены с тактовой шиной 31. Тактовые входы всех сту467477

25 зо

55 50 бй пеней накопителя через шины 32 — 35 соединены с коммутатором 36 тактов, который входами соединен с тактовыми шинами 37 — 40.

Устройство 41 управления накопителем входом 42 соединено с приемником, входом 43— с печатающим устройством, выходом 44 — с коммутатором 36 тактов и дешифратором 45, выходами 46 — 49 — с ком мутатором 36 тактов, входами 50, 51 — с тактовыми шинами.

Выходы всех элементов 1 — 20 памяти соединены со входами дешифратора 45, а его выход соединен со входом исполнительного устройства 52. Выход последнего элемента памяти

20 соединен с одним из входов полусумматора

53, второй вход которого соединен с выходом одного из промежуточных элементов. Выход полусумматора 53 через инвертор 54 и схему

«И» 55 соединен со входом:первого элемента 1 памятн, Вход с приемника 56 соединен со вторым .входом схемы «И» 55 и входом исполнительного устройства 52. Выходы элементо в последней ступени соединены с печатающим устройством.

Устройство работает следующим образом.

В накопителе находится одна комбинацич, предназначенная для вывода на печать. Устройство 41 управления накопителем (УУ11) постоянно подает сигнал «накопитель занят» на коммутатор 36 тактов, который выдает импульсы с тактовой частотой продвижения информации по ступеням. Однако продвижения информации по ступеням не происходит до тех пор, пока с печатающего устройства не придет синхроимпульс на УУН 41 по входу 43. С приходом синхроимпульса начинается последовательное продвижение информации по ступеням на олин шаг при последовательной подаче тактов на шины 33 — 35 и вывод информации с последней ступени на печатающее устройство.

После приема очередной комбинации из канала с приемника по входам 26 — 30 поступает принятая комбинация, а по входу 42 поступает сигнал записи в первую ступень накопителя.

По этому сигналу по шине 31 поступает такг и происходит запись комбинации в первую ступень накопителя через входные схемы «И»

21 — 25.

В режиме печати такты по шине 32 не подаются.

В случае прекращения приема информации накопитель постепенно освобождается, и после полного освобождения УУН 41 подает постоянно на коммутатор тактов 36 сигнал «1» — накопитель свободен», происходит переключение тактов. Такты запрещаются по шине 31 и появляются на шине 32, благодаря чему возникают логические связи между элементами последней и первой ступеней, а также обратная связь на вход первого элемента 1.

Таким образом, накопитель преобразуется в рекуррентный регистр сдвига, генерирующий последовательность максимальной длины. Начальное состояние регистра в момент полного освобождения определяется наличием «О» во всех элементах памяти. Обратная связь на первый элемент осуществляется через полусумматор 53, инвертор 54 и схему «И» 55, на второй вход которой подается сигнал «1» с приемника по входу 56 при отсутствии приема информации. Так как исходное состояние регистра «О», то его работа возможна только с инвертированием выходного сигнала полусумматора 53 инвертором 54.

Длина последовательности, генерируемой регистром, зависит от общего числа ячеек и числа тактов в этом режиме.

Дешифратор 45 определяет состояние регистра, при котором происходит выдача сигнала на исполнительное устройство, выключающее двигатель.

В момент начала приема и нформации с канала из приемника по входу 56 поступает сигнал «О», по которому исполнительное устройство 52 включает двигатель, если он был выключен, а в первый элемент памяти постоянно записывается «О». За время приема одной комбинации «0» должен заполнить элементы памяти всех столбцов, кроме последнего, в котором может быть заполнен только верхний элемент. После приема всей комбинации сигналом по выходу 44 происходит переключение тактов, появление такта на шине 31, запрет тактов на шине 32, запись в первую ступень комбинации из приемника через схемы

«И» 21 — 25.

Запрет тактов на шине 32 переводит усгройство в режим накопителя. С целью исключения ложного выключения двигателя при случайном наборе дешифрируемой комбинации из принимаемой информации на дешифратор 45 подается сигнал «накопитель занят» с УУН 41.

Предмет изобретения

Накопитель-счетчик, содержащий матрицу элементов памяти, устройство ч правления накопителем, соеди ненное с коммутатором тактов, и исполнительное устройство, соединенное со входом управления приемом, причем в столбце выход каждого элемента памяти соединен со входом последующего элемента памяти, входы элементов памяти каждой строки соединены с выходами коммутатора тактов, входы элементов памяти первой строки соединены с шинами входных сигналов, отличаюи1ийся тем, что, с целью упрощения устройсгва, выход элемента памяти каждого столбца последней строки соединен с первым дополнительным входом элемента памяти первой строки следующего столбца, выход элемента памяти последнего столбца последней строки соединен с первым входом дополнительного полусумматора, второй вход которого соединен с выходом одного из элементов памяти, выход полусумматора соединен через вновь введенный инвертор с первым входом дополнительного вентиля, второй вход которого соединен со входом управления приемом, а выход — с первым дополнительным входом элемента памяти первой строки первого столбца, вторые

467477

Составитель И. Разинова

Техред T. Миронова Корреитор А. Дзесова

Редактор Т. Янова

Заказ 4259 Изд. № 1347 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Обл. тип. Костромского управления издательств, полиграфии и книжной торговлв дополнительные входы элементов памяти первой строки соединены с дополнительным выходов коммутатора тактов, выходы всех элементов памяти соединены со входами вновь введенного дешифратора, выход которого соеди» нен со входом ясполнительного устройства,