Цифровой коррелятор

Иллюстрации

Показать всеРеферат

Фыф(реоз

) аятЕНП;0;.,Жлю

"@ ала < тфк»

ОП NCAHN

Союз Советских

Социалистимеских

Республик (11) 468247 (я)дополнительное к авт, свид-ву №-(51) М. Кл.

Q 06 Г 15/34 (22) Заявлено 05.02.74 (21) 1993861! 18-24 с присоединением заявки №Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23)Приоритет

Опубликовано 25.04.75. Бюллетень № 15

Дата опубликования описания 11 О5 75 (БЗ) тД 681.332:519. .2 (088.8) В. С, Гладкий и А. Г. Ермаков (72) Авторы изобретенпя (71) Заявитель

Морской гидрофизический институт AH Украинской CCP (54) ЦИФРОВОЙ КОРРЕЛЯТОР

Изобретение относится к.спепиализированHblM средствам цифровой вычислительной техники, предназначенной для анализа случайных процессов.

Известны цифровые корреляторы, содер5 жащие четыре блока динамической памяти, первый из которых подключен к входу устройства, выход первого блока динамической памяти подключен к входу второго блока и к одному иэ входов первого блока умиоже10 ния, выход второго блока динамической памяти подключен к одному из входов второго блока умножения и к переключателю, соединенному с приемным регистром; выходы которого подключены ко вторым входам обоих

i5 блоков умножения, соединенных соответственно с входами первого и второго накопителей текущих произведений, выходы первого и второго блоков динамической памяти

2и соединены соответственно со своими входами.

Известные устройства характеризуются малым быстродействием при последовательной обработке информации, 25 т.1ель изобретения — повышение быстродействия, Для этого в предлагаемом корреляторе выходы первого и второго накопителей текущих произведений подключены соответственно к входам третьего и четвертого блоков динамической памяти, выходы которых подключены соответственно ко вторым входам первого и второго накопителей текущих произведений.

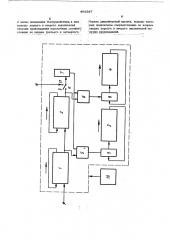

На чертеже изображена структурная схема предлагаемого цифрового коррелятора.

Устройство содержит блоки 1 и 2 динамической памяти, реализующие меняющуюся временную задержку значений входного процесса и построены на сдвиговых регистрах; блоки 3 и 4 динамической памяти, служащие для накапливания и хранения значений корреляционной функции и также построены на регистрах сдвига; блоки 5 и 6 умножения (цифровые); приемный регистр 7, накопители 8 и 9 текущих произведений, блок управления 1.0, переключатель 1 1. режимов работы, имеющий два положения а и б (положение а соответствует режиму вычисле-

4 8247

4 ния автокорреляционной функции, положе- Вновь поступившая кодированная ордината ние б — взаимной корреляционной функции процесса записывается в первую ячейку ло- исследуемых цроце ооцеосор ) . ка 1 а в регистр 7 записывается вторая

К оррелятор ра ботает сдедующим обра- ордината. В остальном второй вычислитель- :. зом.

5 . ный цикл протекает аналогично первому, Ko-, aIIoM работы с помощью бло- :личество вычислительных циклов Равно Я-g, Перед началом р ка управления пр.

10 риемнь-й регистр 7 . где К вЂ” когплчество обработанных значени з о6а накопителя 8 и 9 и блоки 1-4 устанав-, случайного процесса,, я, — суммарное колиливаются в нуль, а переключатель 11 - в " . чество ячеек памяти в блоках 1"й2. Коли-. 6 чество ячеек в блоках 1 и 2 одинаково

В некоторые тактовые моменты времени и равно iA/2, количество ячеек в блоках

Я вЂ” 1/2 текущие значения исследуемого процесса по- (3 и 4 также одинаково и равно даютсЯ в виде паРаллельного двоичного иода После окончания вычислительного процес-, на вход блока 1..эти значения продвигают- са содержимое блоков 3 и 4 может быть ся по олоку 1 и далее "î блоку 2 до того . :считано с выходов путем циклического его

i5, момента, пока пеРвое из значений кода вы- продвижения по блокам 3 и 4 и представляборки процесса не зафиксируется одновремен- ет собой дискретнЫе еняиищя горреляционно на приемном регистре 7 и в последней ной функции исслвдуемо о ро,е„.са с точ ячейке блока 2, после чего подача коди«: ностью до постоянного ь иожителя. рованных ординат процесса прекращается

Процесс вычислекий взаимной корреляции начинается процесс обработки уже посту- онной функции аналогичен описанному и отпившей информации. Блок управления 10, личаетс;я тем, что переключатель 11 уставырабатывает сигнал, по котоРомУ происхо- навливается в положение б, а значения втодит пеРемножение содержимого регистра 7 рого случайного процесса подаются на сс и двух последних ячеек памяти блоков 1 и 2. ответствующий вход коррелятора.

Полученные произведения с выходов блоков В предлагаемом цифровом корреляторе: умножения 5 и 6 записываются в накопите- вычислительный процесс протекает вдвое ли 8 и 9 соответственно. На этом завер- быстрее, чем в известных устройствах по-, шаетсЯ пеРвый шаг пеРвого вычислительно- следовательного типа. Разбивая блок дина-, го цикла. На втоРом шаге в каждом блоке мической памяти на большее число частей

ЗО

1 динамической памяти производится сдвиг и добавляя соответствующее число множина один РазРЯд впРаво. ПРи этом содеРжи- тельных устройств и накопителей, можно мое последних ячеек блоков 1 и 2перепи- еще больше ускорить вычислительный просывается в их первые ячейки, Содержимое цесс, доведя его в пределе до полностью приемного регистра 7 не меняется. Содер- параллельного.

35 жимое накопителей 8 и 9 переписывается

B первые ячейки блоков 8 и 4 соответственно, а в накопители записывается инфор-, Ц р е д м е т изобретения

1 мация (пока нулевая) из соответствующих последних ячеек блоков 3 и 4. После этого

4О

)цифровой коррелятор, содержащий четыв соответствии с сигналом, вырабатываемым ре блока динамической памяти, первый из блоком управления 10, опять производится которых подключек к входу устройства, выперемножение содержимого регистра 7 и ход первого волока динамической памяти последних Ячеек блоков 1 и 2. ПолУченные подключен к входу второго блока и к одноЯ пРоизведениЯ снова записываютсЯ в накопи му из входов первого блока умножения, тели 8 и 9, На этом заканчивается второй выход второго блока динамической памяти: шаг IiePBoiо вь числительн ого цикла. Рет и подключен к одному из входов второго блои все последующие шаги аналогичны второ- ка умножения и к переключателю, соединенму, Первый вычислительный цикл завеР- ному с приемным регистром, выходы кото50 шаетсЯ к томУ моментУ времени„когда ин- рого подключены ко вторым входам оооих формация в блоках 1 л 2 будет находиться блоков умножения, соединенных соответств том же состоянии, что и в начале пеРво- венно с входами первого и второго накопи« го и ага. Вслед за этим на вход коррелятора :телей текупщх произведений, выходы первоподается следующее по порядку значение го и второго блоков динамической памяти г 50 случайного процесса. При этом в блоки 1и2 соединены соответственно со своими вхопроизводится сдвиг на один разряд вправо, дами, о т JT и ч я ю Ill и и е я тем, что, 4682 47

5 с иелью повышения быстродействии,в нем выходы первого и второго накопителей текущих произведений подключены соответ-, ственно ко входам третьего и четвертого

Ъ блрков динамической памяти, выходы кото рых подключены соответственно ко вторым входам первого и второго накопителей те куших произведений.