Преобразователь код-аналог

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Соеетских

Расаублик (11) 468369 (61) Зависимое от авт, свидетельства (22) Заявлено 22.01.73(2Ц 18762О9/26 21 с присоединением заявки (32} Приоритет

Гесударстеаивв кеиетет

Севета Иеееатрее ЫВР па делам юебретеннй и еткфепме (53) Уд 681.325 (088,8) Опубликовано 25.04.75. Бюллетень № 15

Дата опубликования описания 3О О5.75 (72) Авторы изобретения

В. Ф, Одиноков и Ю. И. Малинин (7! ) Заявитель

Рязанский радиотехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ КОД-АНАЛОГ

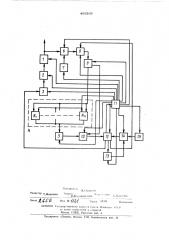

Для этого в преобразователь код-аналог введены дополнительные переключатели, регистр памяти, ключевая схема, блок регистров разрядных весов, регистр разности, регистр эталонного кода, причем второй выход схемы сравнения через регистр памяти

; и ключевую схему соединенсо входом матри цы аналоговых элементов, выход преобразователя аналог-код через первый дополни10 тельный переключатель непосредственно и через блок регистров разрядных весов и ! второй дополнительный переключатель соединен со входами вспомогательного регистра веса, третий выход схемы сравнения чеI

15 рез регистр разности и регистр эталонного кода, второй вход которого присоединен к выходу задатчика кода, соединен со вторым входом схемы оран ения, четвертый выход , êîòîðîé подключен ко входу блока синхро2С ниэации, выходы которого соединены с соот,ветствующими входами всех блоков. на чертеже изооражена Элок-схема предтагаемого преобразователя.

Устройство содержит матрицу аналого25 вых элементов 1, ключевую схему 2, ре!

Изобретение может быть использовано в измерительной технике, в системах пре-щ образования и передачи данных.

Известны преобразователи код-аналог, содержащие матрицу аналоговых элементов, переключатель, блок эталонных параметров, преобразователь аналог-код, вспомогатель ный регистр веса, схему сравнения, блок синхрониэацйи и эадатчик кода, причем выход матрицы аналоговых элементов через переключатель, второй вход которого соединен с выходом блока эталонных параметров, соединен с первым входом преобразователя аналог-код, выход вспомогательного регистра веса соединен с первым входом схемы сравнения, первый выход которой сог" единен со вторым входом преобразователя аналог-код, Однако известные устройства имеют малое быстродействие и модуляцию выходного сигнала в процессе установки его нового значения.

Белью изобретения является устранение модуляции выходного сигнала,и повышение быстродействия, (Я) М. Кл. H Oal, 13il

468369

3 гистр памяти 3, блок регистров разрядных весов 4, второй дополнительный переключатель 5, переключатель 6. блок эталоняых параметров 7, преобразователь аналогкод 8, первый дополнительный переключатель 9, вспомогательный регистр веса 10. блок синхронизации 11, схему сравнения12, регистр разности эталонного кода 14 и задатчик кода 15.

Преобразователь работает следуюшим образом.

Вначале производится коррекция харак» теристики преобразователя 8. Для этого сигналом с блока синхронизации 1 1 через переключатель 6 выход блока эталонных параметров 7 подключают ко входу преобразователя 8. В задатчике кода 15/устанавливают код, соответствующий эталонному параметру блока 7. Вход преобразователя 8 через первый дополнительный переключатель 9 соединяют с регистром 10. По сигналу блока 1 1 код блока 15 переводят в регистр 14, а в регистр 10 записывается код с выхода преобразователя 8. Разность кодов с первого выхода схемы сравнения 12 заводится в преобразователь 8. .для коррекции его характеристики, Затем следует этап тарировки матрицы 1. Для этого вы-, I ход матрицы 1 через переключатель 6 соединяют со входом преобразователя 8, выход которого через первый дополнительный переключатель 9 соединяют с блоком реI гистров разрядных весов 4. В блоке 15 устанавливают код 4, подлежаший преЭ образованию, Тарировке подвергаются последовательно все разряды матрицы 1. Дчя этого сначала по сигналу блока 11 все разряды матри.цы, кроме первого (младшего), устанавливают в нуль, первый — в единицу, С выхода преобразователя 8 код Я, соответ1 ствуюший значению9первого разряда матрицы, записывают в регистре первого разряда блока 4. Далее второй разряд матрицы устанавливают в единицу, все остальные-в нуль. Полученный код Щ веса второго разряда с выхода преобразователя 8 записывается в регистр второго разряда блока 4 и т.д, После записи кода веса последнего разряда в блок 4 преобразователь 8 сигналом блока 11 выводится из режилга преобразования, Следующий этап заключается в определении такого набора разрядов матрицы 1., который дает g, соответствуюший заданному коду 1Ч . Для этого по сигналу с блока 1 1 код Ц иэ блока 15 перепи-. сывается в регистр 14,. код ) перепии 4 сывается через переключатель 5,на A. входов в регистр 10. Коды 1Ч и К

В сравниваются в схеме 1 2. Если Й < > N >

Э) с четвертого выхода схемы 12 на вход блока 11 идет сигнал, по.которому стирается число 1 в регистре 10, -ый

-.. †.- разряд регистра 3 устанавливается на нуль, а в регистр 10 через переключатель

i() 5 переписывается код Ч (p,— g )-ro разряда, который вновь сравнивается с кодом N в схеме 12.

Если (Чц N (T>K же (ц и любой другой вес N„)

1Ъ-1 1 то по сигналу с четвертого выхода схемы 12 блоком синхронизации 11 в регистр 13 записывается код разности (Ч—

Э

-Я ), стираются коды в регистрах 10 и

14, код из регистра 13 переписывается в регистр 14, à h -ый разряд 3 устанавливается в единицу. Далее в регистр 1Ь переписывается код М т, 1 (<- 1) -го . разряда и процесс сравнения продолжается. Сравнцваются уже коды N 1,,и (МЭ вЂ” М ) °

Если Ь(1 — (так же, как и любой другой код („. ),. 11 — ый разряд регистра 3 устанавливается в единицу, все последуюшие (младшие, чем (Ч или Я устанавливаются в нуль.

После этого сигналом блока 11 код регистра 3 через ключевую схему 2 переписывается в матрицу. 1 °

В процессе определения состояния регистра 3 состояние матрицы 1 не изме,няется, т.е. после перезаписи кода из регистра 3 в матрицу 1 значение ме-

40 няется от предыдущего сразу на последующее, минуя промежуточные стадии. Таким образом, преобразование f4

Э происходит без паразитной модуляции выходного сигнала Y .

Подсчитаем количество циклов, необходим ы х для прео бра зог ани я 1Ч Э = Й э эванс

В этапе тарировки требуется Я циклов для преобразования и записи в блок

4 кодов N " . 1Ч тг В этапе поиска бО состояний регистра 3 .в худшем случае не-, обходи го " 11. циклов сравнений (по чис- лу разрядов матрицы 1). В итоге общее число циклов в предлагаелгом устройстве

n1 = ZrL

Выигрыш в быстродействии по сравнению с известным устройством

Щ 2к1 211 1 ° о

468369

Таким образом, предлагаемое устройство более быстродействующее и не имеет паразитной модуляции выходного сигнала.

Предмет изобретения

Преобразователь код-аналог, содержаший матрицу аналоговых элементов, переключатель, блок эталонных параметров, преобразователь аналог-код, вспомогательный регистр веса, схему сравнения, блок синхронизации и задатчик кода, причем выход матрицы аналоговых элементов через переключатель, второй вход которого соединен с выходом блока эталонных параметров, соединен с первым входом преобразователя аналог-код, выход вспомогательного регистра веса соединен с первым входом схемы сравнения, первый выход которого соединен со вторым входом преобразователя аналогкод,отличающийся тем,чтос

М .. целью устранения модуляции выходного сигнала и повышения быстродействия, в него введены дополнительные переключатели, регистр памяти, ключевая схема, блок регис5 тров разрядных весов, регистр разности, регистр эталонного кода, причем второй выход схемы сравнения через регистр памяти и ключевую схему соединен со входом матрицы аналоговых элементов, выход npel0 образователя аналог-код через первый дополнительный переключатель непосредственно и блок регистров разрядных весов и второй дополнительный переключатель соединен: со входами вспомогательного регистра веса, 15 третий выход схемы сравнения через регистр разности и регистр эталонного кода, второй вход которого соединен с выходом

1 задатчика кода, соединен со вторым вхо0 дом схемы сравнения, четвертый выход ко2О торой подключен ко входу блока синхронизации, выходы которого соединены с соответ- ствуюшими входами всех блоков.

46Ь369

Составите I Ii

j1 () (ни нг ив

Техред 1(>, i t. 1 ы

И Кп1 !Щсншэнн

Редактор 1 фадеева

Заказ (Ивд @ Я(ти

Подписное

Предприятие «Патент>, Москва, Г-SQ, Бережковская наб., 24

Ц11ИИПИ Государственного коми в(а Сош I а Мивисгро (.(.:(.,Р

IJo делим изобретений и ыкрьпий

Москва, 1!3035, Раугпская наб., 4