Двоичный счетчик импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

И аетОРСКОМ СВИДЕТЕЛЬСТВ

Союз Советских

Социалистических

Республик (11) 468374 (61) Исполнительное к авт. свид-ву— (22) Заявлено 07.01.72 (21)1736445/26 21 (51) М. Кл.

Н 03к 21/34 с присоединением заявки ме

Гасударственный комитет

Совета Министров СССР по делаи изобретений и открытий (23)Приоритет—

Опубликовано 25 04 75. Бюллетень -15

Дата опубликования описания 30 05 75 (5З) удК 681.326.0 (088.8) E. И. Жуков, Г. В. Никулин и О. С. Горбачев (72) Авторы изобретения (7!) Заявитель (54) ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

Изобретение относится к радиотехнике и может быть использовано в устройствах вычислительной техники.

Известен двоичный счетчик импульсов с контролем ошибок, содержащий разрядные пересчетные ячейки на двух триггерах и.. вентилях записи, входную шину единичного сигнала и выходную шину контрольного счетчика.

Однако известное устройство обладает 10 низкой достоверностью работы и не дает возможности определения места неисправности.

Целью изобретения является повышение достоверности работы счетчика и определе- 15 ние места неисправности.

Для этого в нем дополнительно установлены схема задержки, формирователь и обшая схема совпадения, а в каждом разряде счетчика установлены транзисторный каскад, 2О сравниваюшая схема, два инвертора и две схемы совпадения, причем вход счетчика соединен с вентилями записи одного триггера каждой пересчетной ячейки, с одним входом формирователя и входом схемы задерж- 25 ки, выход которой подключен к вентилям записи другого триггера каждой пересчетной ячейки и к другому входу формирователя, выход которого соединен с эмиттерным входом транзисторного каскада первой пересчетной ячейки, выходы двух триггеров каждой пересчетной ячейки соединены со сравниваюшей схемой этой же ячейки, выход которой подключен к одному входу одной схамы совпадения и одному инвертору, выход которого подключен к одному входу другой схемы совпадения, вьсходы обеих схем совпадения соединень1 с входами обшей схемы совпадения, внхсд которой подсоединен к выходнои шине контроля счетчика, вторые входы одной и другой схем совпадения соответственно через другой инвертор и непосредственно соединены с коллекторным выходом транзисторного каскада, соединенным с эмиттерным входом транзисторного каскада последующего разряда, базовые входы транзисторных каскадов всех пересчетных ячеек, кроме первой, соединены с выходом другого триггера предыдущей пересчетной ячейки, à базовый вход транзисторного каскада первой

468374 го обстоятельства осуществляется при помощи сравнивающих схем 14-1 — 14--Й, П и этом с соответствующих транзисторных р каскадов 13-1 - 13-Ф поступает нулевой сигнал, который открывает схемы совпадения 17- — 17- Ь.Если запись в триггеры

2-- 2- Всоответствуюших пересчечных яче» ек прошла правильно,то со сравнивающих схем

14-1 — 14- ф снимаются нулевые сигналы,; оторые через инверторм 15-1 — 15- закрывают схемы совпадения 17-1 — 17- .

Если при записи возникли ошибки, то с одной или нескольких сравнивающих схем

14-1 — 14- Ц снимается единичный сигнал, который проходит через схемы совпадения 17-1 — 17- tl, и через схему совпадения 12 поступает на выходную шину конт роля 9, Одновременно может быть снята информация с выходов схем совпадения

17-1 - 17- tl, Эта информация позволяет локализовать место возникновения ошибки с точностью до одной пересчетной схемы.

Так KGK сигналы записи в триггеры разделены во времени, то правильность записи в триггеры 3-1 - 3- П, производится ана-. логичным образом. При этом с выходов транзисторных каскадов 13-1 — 13- fL снимается единичный сигнал и производится контроль триггеров. Их состояния должны быть одинаковыми, При одной или нескольких ошибках сигналы со сравнивающих схем 14-1 — 14- tt, поступают через схемы совпадения 18-1 - 18-3ъ на схему совпадения 12, а с нее — на выходную шину контроля 9. разрядные пересчетные ячейки 1-1 — 1- на триггерах 2-1 — 2- 11 и 3-1 — 3- tl,, вентилях 4-1 — 4- tl, 5-1 — 5-М, 6-.1—

-6- g и 7 1 — 7- 1,, входную шину единичного сигнала 8 и выходную шину контр - 0 ля 9 счетчика.

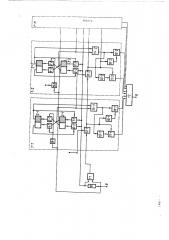

На чертеже ячейки l- tl, не раскрыта, показано только две ячейки — 1-1 и 1-2.

В двоичный счетчик импульсов входят также схема задержки 10, формирователь 11 и схема совпадения 12.

В разрядных ячейках 1-1 — 1- 1 установлены соответственно транзисторные каскады 13-1 — 13- tl, сравнивающие схемы .,!0

14-1 — 14- tl, инверторы 15-1 — 15- tl, 16-1 — 16- и,, схемы совпадения 17-1—

17- tL, 18-1 — 18- tl и инверторы.19-1

19- tt .

Двоичный счетчик импульсов работает следующим образом.

На входную шину 8 поступают импульсы счета, Эти импульсы подаются Hs триггеры 2-1 - 2- П, проходят через схему задержки 10 и поступают на триггеры 3-13- tl, . Импульсы триггеров 2-1 — 2- П

30 и 3-1 — 3- tl оказываются смещенными друг относительно друга.

Импульсы с входа и выхода схемы задержки 10 поступают на. формирователь 11, вырабатывающий импульсы, длительность

35 которых равна интервалу между сдвинутыми импульсами.

Сигнал с выхода формирователя 11 поступает на эМиттерный вход транзисторного каскада 13- . Базовые входы транзисторт

40 ных каскадов 13-1 — 13-tl соединены с выходами триггеров:,.3-1 — 3- И .

Транзисторные каскады 13-1 - 13- и образуют цепочку пос;едовательно соединен45 ных транзисторов, у которых коллектор предыдущего (младшего) каскада с .оединен с эмиттером последующего (старшего) каскада соответствующих пересчетных ячеек

1-1 — 1- tl.

При действии импульсов записи через инверторы 19-1 - 19- tl, в зависимости от состояния пересчетных ячеек 1-1 - 1-71 в триггеры 2- 1 - 2- записываются инверсные состояния триггеров 3-1 -3- 1, .

55 аким образом, в этот момент в пересчетных ячейках 1-1 - 1- tl, состсяния триггеров должно быть разными. Проверка это3 пересчетной ячейки соединен с входной ши1 о ". единичного сигнала.

На чертеже приведена блок-схема устройства.

Двоичный счетчик импульсов содержит.

Предмет изобретения

Двоичный счетчик импульсов с контролем ошибок, содержащий разрядные пересчетные ячейки на двух триггерах и вентилях записи, входную шину единичного сигнала и выходную шину контроля счетчика, отличающийсятем, что,сце лью повышения достоверности работы и определения места неисправности счетчика, в нем дополнительно установлены схема задержки, формирователь и общая схема совпадения,а в каждом разряде счетчика установлены транзисторные каскады, сравнивающую схему, два инвертора и две схемы совпадения, причем вход счетчика coüединен с вентилями записи одного триггера каждой пересчетной ячейки, с одним входом формирователя и входом схемы задержки, выход которой подключен к вентилям записи другого триггера каждой пере458374 счетной ячейки и к другому входу формиро= вателя, выход которого соединен с эмиттерным входом транзисторного каскада первой пересчетной ячейки, выходы двух триггеров каждой перэсчетной ячейки соединены со сравнивающей схемой этой же ячейки, выход которой подключен к одному входу одной схемы совпадения и одному инвертору, выход которого подключен к одному входу другой схемы совпадения, выходы обеих схем совпадения соединены с входами общей схемы совпадения, выход которой подсоединен к выходной шине контроля сче чика, вторые входы одной и другой схем совпадения соответственно через другой инвертор и непосредственно соединены с коллекторным выходом транзисторного ка5 скада, соединенным с эмиттерным входом транзисторного каскада последующего разряда, базовые входы транзисторных каска дов всех пересчетных ячеек, кроме первой, соединены с выходом другого триггера пред дыдущей пересчетной ячейки, а базовый вход транзисторного каскада первой пересчетной ячейки соединен с входной шиной единичного сигнала.