Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

: -.::.:.и ж 1 т н Иа

Опислни, g s () @ P E T F:. н и ) иц 4692 07

Сок)з Ссеетских

Соннанистнч:."»11»

Россу "";ss

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства

is)) v. Кл. н os) siss (22) Заявлено 16.06.72 (21) 1799763/26-9

I с присоединением заявки ¹

Совета Ии)1))с-.-as СССР по денем нзабретеннй н открытий

)М) УДК 621.375.024! Опубликовано 20.04.75. Бюллетень ¹ 16 !

Дата опубликсвания описания 05.08,75 (72) Автор изобретения

В. В. Матавкин

Рижский научно-исследовательский институт микроприборов (71) Заявитель (54) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ

ГосУдаРстееннмй комитет (2) Пр ор

Изобретение относится к усилителям и может использоваться при построении входных каскадов в схемах многокаскадных усилителей, например операционных усилителей.

Известен дифференциальный усилитель, содсржащий последовательно соединенные входной балансный каскад на транзисторах, включенных по схеме с общим коллектором, в цепи эмиттеров которых введены генераторы тока, и выходной балансный каскад, выполненный на транзисторах противоположного типа проводимости, включенных по схеме с общим эмиттером, общая эмиттерная цепь которых через последовательно соединенные транзистор в диодном включении и генератор тока г)одключена к соответствующей шине источника питания.

Цель изобретения — стабилизация режима работы транзисторов.

Это достигается тем, что в предлагаемом усилителе в общую коллекторную цепь транзисторов входного каскада введен дополнительный транзистор, база которого подключена к месту соединения упомянутых транзистора в диодном включении и генератора тока выходного каскада.

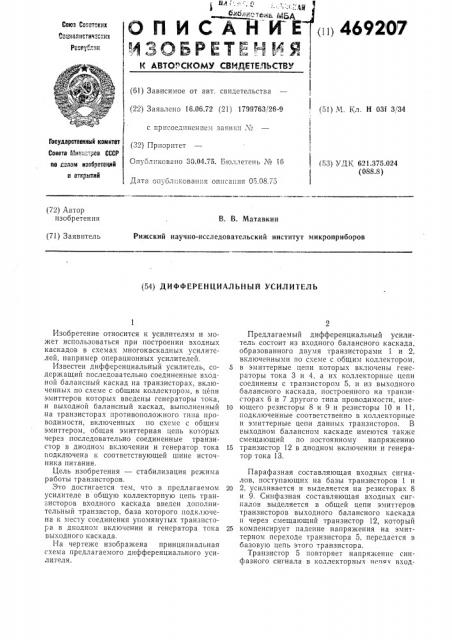

На чертеже изображена принципиальная схема предлагаемого дифференциального усилителя.

Предлагаемый дифференциальный усилитель состоит из входного балансного каскада, образованного двумя транзисторами 1 и 2, включенными по схеме с общим коллектором, 5 в эмиттерные цепи которых включены генераторы тока 3 и 4, а их коллекторные цепи соединены с транзистором 5, и из выходного балансного каскада, построенного на транзисторах 6 и 7 другого типа проводимости, име1о ющего резисторы 8 и 9 и резисторы 10 и 11, подключенные соответственно в коллекторные и эмиттерные цепи данных транзисторов. В выходном балансном каскаде имеются также смещающий по постоянному напряжению

15 транзистор 12 в диодном включении и генератор тока 13.

Парафазная составляющая входных сигналов, поступающих на базы транзисторов 1 и

20 2, усиливается и выделяется на резисторах 8 и 9. Синфазная составляющая входных сигналов выделяется в общей цепи эмиттеров транзисторов выходного бал ансного каскада и через смещающий транзистор 12, который

25 компенсирует падение напряжения на эмиттерном переходе транзистора 5, передается в базовую цепь этого транзистора.

Транзистор 5 повторяет напряжение синфазного сигнала в коллекторных непях вход469207

Предмет изобретения

Составитель Н. Герасимова

Редактор Е. Караулова Техред Т. Миронова

Корректор И. Позняковская

Заказ 1903/12 Изд. Из 1409 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ных транзисторов. Выбором величин сопротивлений резисторов 8 и 9 и тока генератора тока 13 устанавливается определенная величина падения напряжения на коллекторных переходах входных транзисторов, В частном случае может быть выбрано нулевое падение напряжения на коллекторных переходах входных транзисторов. Установленная величина падения напряжения на коллекторных переходах этих транзисторов сохраняется постоянной при широких изменениях значений синфазной составляющей входных сигналов. Объединение коллекторных цепей транзисторов входного балансного каскада и отделение их с помощью транзистора 5 от цепи выделения синфазного сигнала позволяет осуществить одинаковые электрические режимы транзисторов дифференциального усилителя, что приводит к улучшению балансных свойств в целом всего усилителя.

Дифференциальный усилитель, содержащий последовательно соединенные входной баланс5 ный каскад на транзисторах, включенных по схеме с общим коллектором, в цепи эмиттеров которых введены генераторы тока, и выходной балансный каскад, выполненный на транзисторах противоположного типа проводимоl0 сти, включенных по схеме с общим эмиттером, общая эмиттерная цепь которых через последовательно соединенные транзистор в диодном включении и генератор тока подключена к соответствующей шине источника питания, от15 л и ч а ю шийся тем, что, с целью стабилизации режима работы транзисторов, в общую коллекторную цепь транзисторов входного каскада введен дополнительный транзистор, база которого подключена к месту соединения

20 упомянутых транзистора в диодном включении и генератора тока выходного каскада.