Множительное устройство

Иллюстрации

Показать всеРеферат

О П- IA©-:А "Н И Е

ИЗОБРЕТЕН ИЯ (i ) 46997Î

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 05.02.73 (21) 1880774/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.05.75. Бюллетень № 17

Дата опубликования описания 30.07.75 (51) М. Кл. б 06! 7 52

Государственный комитет

Совета Министров СССР (53) УДК, 681 142(088 8) по делам изобретений и открытий (i2) Лвторы изобретения

В. В. Владимиров, L . И. Духнич и И. Ф. Сурженко

1 аганрогский радиотехнический институт (71) Заявитель (54) MHONИ f ЕЛЬНОЕ УС 1 РОЙСТВО

Изобретение относится к области цифровой вычислительной технике и используется при построении последовательно-параллельных цифровых вычислительных устройств.

Известно множительное устройство, содержащее М-разрядный регистр множителя, Л разрядный регистр множимого, соединенный со входами блока формирования чисел, кратных множимому, блок образования частичных произведений множимого на два разряда множителя одновременно, первые входы которого соединены с соответствующими выходами блока формирования чисел, кратных множимому, а вторые — с выходами регистра множителя, и однотактные элементы задержки (на чертеже обозначены / и+2 и j.n+3 (/ = 5, 6, ..., М/2 (-3) .

Недостатком такого устройства является его сложность при последовательно-параллельной обработке информации.

Целью изобретения является упрощение устройства при последовательно-параллельной обработке информации.

Поставленная цель достигается за счет то го, что устройство содержит М/2 сумматоров частичных произведений, каждый из которых состоит из n (n — число одновременно-обрабатываемых разрядов множимого) одноразрядных комбинационных сумматоров и элемента задержки. Выходы блока образования частичных произведений соединены соответственно с первыми входами одноразрядных комбинационных сумматоров, выход суммы j ко одноразрядного комбинационного сумматора

5 (j = 5, 6, ..., М/2+3; = 1, 2, ..., n — 2) соединен непосредственно со вторым входом j + 1, /-т-2-го одноразрядного комбинационного сумматора, а выходы суммы / n — 1-го и j u-ro одноразрядных комоинационных сумматоров

10 соединены со вторыми входами j+1 ° 1-ro u

1 + 1 2-ro одноразрядных комбинационных сумматоров соответственно через однотактные элементы задержки /.и+2 и и+3. Выход переноса j.i-ro одноразрядного комбинацион15 ного сумматора (j=5, b, ..., М/2+4; i=1,2, ..., и — 1) соединен непосредственно со входом переноса j i+1-го одноразрядного комбинационного сумматора, а выход переноса j и-го одноразрядного комбинационного сумматора

20 соединен со входом переноса 1.1-ro одноразрядного комбинационного сумматора через однотактный элемент задержки j n+1.

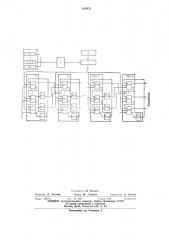

На чертеже дана схема устройства.

В состав множительного устройства входяг

25 N-разрядный регистр множимого 1, содержащий и параллельно работающих И/и-разрядных частей 1.1 — 1.и, блок 2 формирования чисел, кратных множимому; М-разрядный регистр 3 множителя; блок 4 образования ча30 стичных произведений на два разряда мно469970

3 жителя одновременно; сумматоры 5, 6, М/2+4 частичных произведений, каждый из которых содержит по п одноразрядных комбинационных сумматоров 5 1 — 5 п, 6 1 — 6.п, М/2+4.1 — М/2+4 п и по элементу задержки

5 п+ l и 6.n+ 1.

Кроме того, устройство содержит однотактные элементы задержки 5 п+2, 6.u+2— — М/2+3 п+2, 6 и+3 — М/2+З.n+3.

Устройство работает следующим образом.

В регистр множимого заносится множимое, в регистр множителя — множитель. Информация в регистре множимого 1 размещается таким образом, чтобы в каждом такте сдвига на выходе регистра появились п очередных разрядов информации, причем младший разряд размещается в части 1 ° 1, и-и — в части 1 п.

По сдвигающим импульсам множимое одновременно п разрядами из регистра 1 поступает на блок формирования чисел 2, кратных множимому. Множимое, его удвоенное и утроенное значения также одновременно п разрядами поступают на блок образования частичных произведений множимого 4 на два разряда множителя одновременно, где в каждом такте работы устройства формируется п М/2 частичных произведений, поступающих на входы сумматоров /.i (j=5, 6, ..., М/2+4; (=1, и — 1, п). На сумматорах j производится суммирование частичных произведений, и на выходе множительного устройства в каждом такте умножения появляется п очередных разрядов произведения.

У-)- М

Время умножения составляет тактов. п

Предмет изобретения

Множительное устройство, содержащее Мразрядный регистр множителя, N-разрядный регистр множимого, соединенный со входами блока формирования чисел, кратных множимому, блок образования частичных произведений множимого на два разряда множителя одновременно, первые входы которого соединены с соответствующими выходами блока формирования чисел, кратных множимому, а вторые входы — с выходами регистра множителя, и однотактные элементы задержки

/ и+2, / и+3 (j =5, 6, ..., M 2+3), отл и ч а ю10 щ е е с я тем, что, с целью упрощения устройства при последовательно-параллельной обработке информации, оно содержит М/2 сумматоров частичных произведений, каждый из которых состоит из п (и — число одновременно

15 обрабатываемых разрядов множимого) одноразрядных комбинационных сумматоров и элемента задержки; причем выходы блока образования .частичных произведений соединены соответственно с первыми входами однораз20 рядных комбинационных сумматоров, выход суммы j i-го одноразрядного комбинационного сумматора (= 5, 6,, М/2+3; i = 1, 2, ..., п — 2) соединен непосредственно со вторым входом j+1, i+2-го одноразрядного комбина25 ц ионного сумматора, а,выходы суммы j.n — 1. го и 1 . и-ro одноразрядных комбинационных сумматоров соединены со вторыми входами

j+1 1-го и /+1 2-ro одноразрядных комбинационных сумматоров соответственно через

30 однотактные элементы задержки j п+2 и

j п+3; выход переноса / i-ro одноразрядного комбинационного сумматора (j = 5, 6, М/2+4; i = 1, 2,, п — 1) соединен непосредственно со входом переноса j i + 1-ro однораз35 рядного комбинационного сумматора, а выход переноса j u-ro одноразрядного комбинационного сумматора, а выход переноса j п-го одноразрядного комбинационного сумматора соединен со входом переноса /.1-ro однораз40 рядного комбинационного сумматора через однотактный элемент задержки 1 п+1.

469970

Составитель В. Захаров

Техред М. Семенов

Корректор Л. Котова

Редактор Л. Утехина

Типография, пр. Сапунова, 2

Заказ 1857/4 Изд. ¹ 680 Тираж 679 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5