Устройство для контроля логических узлов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ («) 46997!

СОюз Советскид

Содиалистииеских

PGcil сиик (61) Дополнитсльное к авт. свид-ву (22) Заявлено 13.12.73 (21) 1975746/18-24 с присоединением заявки № (51) М. Кл. 6061 11 00

Совета Ыииистров СССР ав делам изобретений и открытий

Опубликовано 05.05.75. Бюллетень № 17

Дата опубликования описания 30.07.75 (53) УДК 681.;:7(088.8) (72) Авторы изобретения

А. В. Карлов, А. Д. Бакакин и В. И. Дорохин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ

ГосУАаРствениый комитет (23) Г1риоритет

Устройство относится к области вычислительной техники, в частности к системам программного контроля.

Известны устройства для контроля логических узлов, содержащие блок оперативной памяти, адресный коммутатор, блоки генерации и коммутации стимулирующих воздействий, блок выявления неисправностей, блок анализа неисправностей и логической обработки и блок управления.

Однако известные устройства не обеспечивают достаточной точности и полноты контроля в реальных условиях с установлением области устойчивой работы объекта проверки.

Целью изобретения является устранение этих недостатков и расширение функциональных возможностей устройства.

Эта цель достигается тем, что устройство дополнительно содержит блок памяти неисправностей, соединенный выходом с блоком выявления неисправностей, а выходом — с блоком анализа неисправностей и логической обработки, один выход которого подключен к блоку управления и четыре выхода через адресный коммутатор — к блоку оперативной памяти.

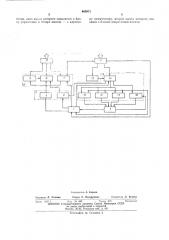

Структурная схема устройства представлена на чертеже.

Устройство содержит блок оперативной памяти 1; адресный коммутатор 2; блок управления 3, включающий в себя блок задания порядка следования 4 и блок задания времени

5; блок генерации стимулирующих воздействий 6, состоящий из блока формирования кодовых комбинаций 7, генератора чисел 8 и блока преобразования код — аналог 9; блок коммутации стимулирующих воздействии 10; блок выявления неисправностей 11; блок памяти неисправностей 12; блок анализа неисправностей и логической обработки 13, состоя10 щий из блока анализа неисправностей и принятия решений 14, регистров подпрограмм 15, сбоев 16, цикла 17 и возврата 18.

Блок оперативной памяти 1 служит для хранения программ контроля и представляет

15 собой ЗУ с произвольным доступом к ячейкам памяти по адресу, задаваемому адресным коммутатором 2.

Блок задания порядка следования 4 служит для расстановки разрядов генератора чисел 8

20 в соответствии с командой блока оперативной памяти 1 и определяет взаимодействие разрядов генератора чисел 8.

Генератор чисел 8 выдает серию комбинаций по закону, установленному блоком зада25 ния порядка следования 4. Генератор чисел 8 может быть выполнен в виде многоразрядного счетчика со сквозным переносом, причем цепи переноса могут подключаться к любым разрядам счетчи à,,что создает возможность пе30 ребора кодовых комбинаций на выходе генера469971

40

65 тора чисел 8 с различным порядком следования.

Блок задания времени 5 и блок преобразования код — аналог 9 служат для установления амплитудно-временных характеристик генератора чисел 8. Блок формирования кодовых комбинаций 7 предназначен для расстановки разрядов в кодовых комбинациях необходимой длины и последовательности при ограниченном числе разрядов в слове блока оперативной памяти 1. Блок формирования кодовых комбинаций 7 может быть выполнен в виде регистра памяти с управляемыми входами и выходами.

Блок коммутации стимулирующих воздействий 10 посылает последовательность кодовых комбинаций на об.ьект проверки (на чертеже не показан).

Блок выявления неисправностей 11 предназначен для установления факта неисправности объекта проверки и определения соответствия программе реакций объекта проверки.

Блок памяти неисправностей 12 служит для накапливания результатов отдельных этапов контроля.

Блок анализа неисправностей и принятия решений 14 определяет характер неисправности и переводит устройство на его локализацию.

Регистры подпрограмм, 15, сбоев 16, цикла

17 и возврата 18 служат для хранения и выдачи адресов блока оперативной памяти 1, по которым необходимо обратиться в соответствии с решением, принятым блоком анализа неисправностей, и принятия решений 14.

Устройство работает следующим образом.

Генератор чисел 8 по команде с блока оперативной памяти 1 через блоки 4, 5 и 9 вырабатывает серию кодовых комбинаций, которые посылает через блок коммутации стимулирующих воздействий 10 на объект проверки, при этом обеспечивается проверка на рабочей частоте объекта проверки независимо от быстродействия блока оперативной памяти 1, Кодовые комбинации реакции объекта проверки накапливаются в блоке выявления неисправностей 11, в котором происходит сравнение по окончании работы генератора чисел накопленной информации с эталонной, поступающей с блока формирования кодовых комбинаций 7. При совпадении накопленной и эталонной информации блок оперативной памяти 1 задает следующий порядок следования воздействий генератору чисел 8 и т. д.

Установление области устойчивой работы производится путем изменения амплитудновременных характеристик стимулирующих воздействий блоками 5 и 9. В этом случае блок анализа неисправностей и принятия решений 14 выдает команду блоку задания порядка следования 4 на многократный перебор кодовых комбинаций генератором чисел 8, а гакже, по адресу, записанному в регистре цикла 17, осуществляет обращение к подпрограмме проверки области устойчивой работы объекта проверки. При несоответствии накоп IcHной и эталонной информации блок анализа неисправностей и принятия решений 14 выраоатывает команду обращения к подпрограмме локализации неисправности через регис- р сбоя 16. Лдрес подпрограммы записывается блоком оперативной памяти 1 в регистр подпрограмм 15. Блок оперативной памяти 1 в этом случае через блоки формирования кодовых комбинаций 7 и коммутации стимулирующих воздействий 10 выдает на объект проверки кодовые комбинации. После выдачи каждого стимулирующего воздействия блок оперативной памяти 1 через блок формирования 7 выдает в блок выявления неисправностей ll эталонный код реакции объекта проверки. Все случаи несоответствия реакций объекта проверки с эталоном фиксируются блоком памяти неисправностей 12. По окончании подпрограммы блок анализа неисправностей и принятия решений 14 определяет вид неисправности и переходит к следующему участку программы по адресу, записанному. ранее в регистре возврата 18 с адресного коммутатора 2 в момент перехода к подпрограмме локализации неисправности.

В случае необнаружения неисправности по подпрограмме блок анализа неисправностей

14 принимает решение о случайном отказе объекта проверки при работе на рабочей частоте, и по адресу, записанному в регистре сбоев 16, устройство переходит к очередному. участку программы.

По окончании всей программы контроля и отсутствии неисправностей объект проверки считается исправным.

Пре Iìåт изобрcтеHèÿ

Устройство для контроля логических узлов, содержащее адресный коммутатор, первый выход которого подключен к первому входу блока анализа неисправностей и логической обработки, блок оперативной памяти, первый и второй выходы которого подключе.- ы к б.".оку управления, третий выход — к первому входу блока генерации стимулирующих воздействий, а четвертый — к блоку анализа и .исправностей и логической обработки, выходы блока управления соединены со вторым третьим входами блока стимулирующих воздействий, три выхода которого подк,.:ючены к блоку, коммутации стимулирующих воздсйствий, а один выход — к блоку выявления неисправностей, выходы которого соединены со вторым входом блока анализа неисправностей и логической обработки и первым входом блока оперативной памяти, о т л и ч а ю щ е ос я тем, что, с целью повышения точности н полноты контроля, устройство дополнительно содержит блок памяти неисправностей, соединенный входом с блоком выявления неисправностей, а выходом — с третьим входом блока анализа неисправностей и логической обра469971

Составитель А. Карлов

Техред Е. Подурушина

Корректор Л. Котова

Редактор Л. Утехина

1857, 5 Изд. № 680 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР пю делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5

Заказ

Типография, пр. Сапунова, 2 ботки, один выход которого подключен к блоку управления и четыре выхода — к адресному коммутатору, второй выход которого соединен с блоком оперативной памяти.