Логический элемент задержки

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 11 470 067

Союз советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 08.06.73 (21) 1930820/26-9 с присоединением заявки № (23) Приоритет (51) М. Кл. Н 03k 5, 13

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий

Опубликовано 05.05.75, Бюллетень ¹ 17 (53) УДК 621,374,5 (088.8) Дата опубликования описания !2.08.75 (72) Авторы изобретения

Д. А. Мнухин и 8. А. Тихомиров

Калининский завод злектроаппаратуры (71) Заявитель (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЗАДЕРЖКИ

Изобретение относится к импульсной технике, может быть использовано в бесконтактных схемах автоматического регулирования.

Известны логические элементы задержки, содержащие входной элемент «ИЛИ вЂ” HE» на р-п-р транзисторе, подсоединенный коллекторо» через резистор связи к базе р-п-р транзистора выходного элемента «ИЛИ вЂ” HE», времязадающую RC-цепь, пороговый каскад, резистивный делитель напряжения, подключенный к базе транзистора выходного элемента

«ИЛИ вЂ” НЕ».

Известные логические элементы имеютнизкую стабильность работы, большое время восстановления. Кроме того, вследствие инерционности порогового каскада на выходе элемента появляется кратковременный импульс в момент подачи сигнала на его вход.

С целью исключения появления выходного сигнала в момент подачи входного сигнала в описываемом логическом элементе между коллектором транзистора входного элемента

«ИЛИ вЂ” НЕ» и резистором связи введен диод в прямом включении. Между точкой их соединения и общей шиной подключен .конденсатор. С целью ускорения восстановления и повышения стабильности длительности задержки пороговый каскад выполнен на транзисторах разных типов проводимости, соединенных по схеме аналого двухбазового диода, подключенного базой р-п-р транзистора через диоды элемента «ИЛИ» к коллекторам элементов «ИЛИ вЂ” НЕ», а эмиттером и-р-и транзистора — к выходу времязадающей КС-цепи.

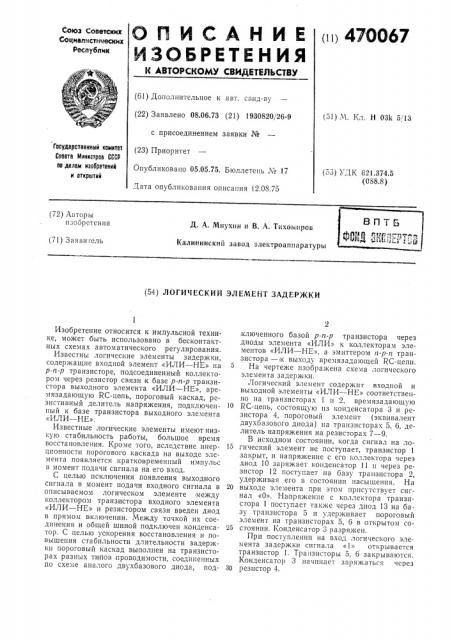

На чертеже изображена схема логпчес«ого элемента задержки.

Логический элемент содержит входной и выходной элементы «ИЛИ вЂ” HE» соответственно на транзисторах 1 и 2, времязадающую

10 КС-цепь, состоящую из конденсатора 3 и резистора 4, пороговый элемент (эквивалент двухбазового диода) на транзисторах 5, 6, делитель напряжения на резисторах 7 — 9.

В исходном состоянии, когда сигнал на ло15 гический элемент не поступает, транзистор 1 закрыт, и напряжение с его коллектора через диод 10 заряжает конденсатор 11 и через резистор 12 поступает на базу транзистора 2, удерживая его в состоянии насыщения. На

20 выходе элемента при этом присутствует сигнал «О». Напряжение с коллектора транзистора 1 поступает также через диод 13 на базу транзистора 5 и удерживает пороговый элемент на транзисторах 5, 6 в открытом со25 стоянии. Конденсатор 3 разряжен.

При поступлении на вход логического элемента задержки сигнала «1» открывается транзистор 1. Транзисторы 5, G закрываются.

Конденсатор 3 начинает заряжаться чсрез

30 резистор 4.

470067

Составитель М. Порфирова

Техред М. Семенов

Корректор В. Брыксина

Редактор Б. Федотов

Заказ 1912 15 Изд. № 705 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4,5

Типография, пр. Сапунова, в

Транзистор 2 удерживается в открытом состоянии током разряда конденсатора 11 через резистор связи 14.

После перехода транзисторов 5, 6, в закрытое состояние транзистор 2 удерживается в открытом состоянии током, переходящим через резисторы 7, 8, переход база-эмиттер транзистора 2. Конденсатор 11 разряжен.

При заряде конденсатора 3 до опорного напряжения делителя (резисторы 7, 8) транзисторы 5, 6 открываются, конденсатор 3 разряжается. Время разряда конденсатора 3 определяет время готовности логического элемента задержки к повторному действию.

Потенциал в точке соединения резисторов

7, 8 становится равным нулю. Транзистор 2 закрывается. Напряжение с коллектора транзистора 2 поступает через диод 14 на базу транзистора 5, удерживая тем самым аналог двухбазового диода в открытом состоянии.

На выходе логического элемента задержки появляется сигнал «1». При снятии сигнала

«1» со входа логический элемент возвращается в исходное состояние.

Предмет изобретения

1. Логический элемент задержки, содержащий входной элемент «ИЛИ вЂ” НЕ» на р-п-р транзисторе, подсоединенный коллектором через резистор связи к базе р-и-р транзистора выходного элемента «ИЛИ вЂ” НЕ», времязадающую RC-цепь, пороговый каскад, резистивный делитель напряжения, подключенный к базе транзистора выходного элемента

«ИЛИ вЂ” НЕ», отличающийся тем, что, с целью исключения появления выходного сигнала, в момент подачи входного сигнала

10 между коллектором транзистора входного элемента «ИЛИ вЂ” HE» и упомянутым резистором связи введен диод в прямом включении, а между точкой их соединения и общей шиной подключен конденсатор.

2. Логический элемент по п. 1, от лича ющи йся тем, что, с целью ускорения восстановления и повышения стабильности длительности задержки, пороговый каскад выполнен на транзисторах разных типов проводимости, соединенных по схеме аналога двухбазового диода, подключенного базой р-п-р транзистора через диоды элемента «ИЛИ» к коллекторам упомянутых элементов «ИЛИ вЂ” НЕ», а эмиттером п-р-и транзистора — к выходу времязадающей RC-цепи.