Запоминающее устройство на интегральных схемах

Иллюстрации

Показать всеРеферат

«;:лч с ..нiY3p

00 47086О

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 24.09.71 (21) 1698551/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15,05.75. Бюллетень ¹ 18

Дата опубликования описания 26.08.75 (51) ß1, Кл. G 11с 11/34

Государственный комитет

Савета Министров СССР па делам изобретений и открытий (53) УДК 681.327.066 (088.8) (72) Авторы изобретения

P. В. Смирнов и Г. В. Виталиев (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО HA ИНТЕГРАЛЬНЬ1Х

СХЕМАХ

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам (ЗУ) на полупроводниковых интегральных схемах.

Известны полупроводниковые интегральные

ЗУ, выполненные в виде набора интегральных накопительных модулей со схемами управления, включая вентили, дешифраторы адреса с основными адресными шинами и управляемые источники питания, которые соединены между. собой с помощью так называемых гибких межсоединений.

Недостаток известных устройств состоит в том, что изготовление ЗУ на интегральных схемах по методу избирательного монтажа подразумевает включение в производственный цикл вычислительной машины и приводит к значительному снижению плотности компановки на пластине с элементарными накопительными модулями, так как непосредственный контроль этих модулей требует введения большого числа дополнительных контактных площадок.

Целью изобретения является увеличение степени интеграции и надежности устройства.

С этой целью каждый модуль содержит регистр, дополнительные вентили и схему сравнения. Входы регистра соединены с доIlîëHèòåëüIIblми адресными шинами, а дешифратор адреса каждого модуля соединен с о."новными адресными шинами через вентили, вторые входы которых подсоединены к выходу схемы сравнения, входы которой подключены к дополнительным адресным шинам и вы5 ходам соответствующего регистра. Входы управляемых источников питания подключены к выходам схем сравнения соответствующих модулей.

Суть изобретения состоит в блокировке об10 ращений к дефектным модулям с помощью соответствующих схем сравнения и регистров.

При этом исправные модули выбираются в соответствии с номерами модулей, которые записаны в их регистрах. Преимуществом дан15 ного устройства по сравненшо с интегральными ЗУ на основе гибких межсоединений является регулярность связей между модулями, что позволяет строить сверхбольшие интегральные ЗУ.

С целью понижения рассеиваемой мощности устройства каждый регистр может содержать дополнительный триггер, вход которого подсоединен к вспомогательным адресным шинам, а один из выходов этого триггера подсоединен ко входу управляемого источника питания соответствующего модуля.

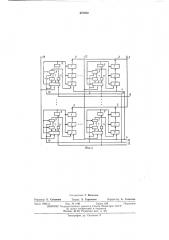

На фиг. 1 приведена блок-схема предлагаемого ЗУ; на фиг. 2 — блок-схема ЗУ с допол30 нительными триггерами.

470860

35

Устройство состоит из элементарных накопительных модулей 1 с дешифраторами 2 адреса, разрядными шинами 3 и основными адресными шинами 4, вентилей 5 и управляемых источников 6 питания. Кроме того, каждый модуль 1 устройства содержит регистр 7, дополнительные вентили 8 и схему 9 сравнения. При этом входы регистра 7 соединены с дополнительными адресными шинами 10, а дешифратор 2 каждого модуля соединен с шинами 4 через вентили 5, вторые входы которых подсоединены к выходу схемы 9 сравнения. Входы каждой схемы 9 подключены к шинам 10 и выходам соответствующего ей регистра 7. Входы управляемых источников 6 подключены к выходам схем 9 соответствующих модулей 1.

Устройство может содержать в каждом регистре 7 дополнительный триггер 11, вход которого подсоединен к вспомогательным адресным шинам 12 через вентили 8, другие входы которых подключены к соответствующим шинам 10. Один из выходов триггера 11 подсоединен ко входу источника 6 соответствующего модуля l. С целью уменьшения количества внешних выводов одноименные шины 3 всех модулей 1 могут быть объединены.

Работа устройства осуществляется следующим образом.

Первоначально выявляются все дефектные модули 1, в регистры 7 которых записывается

«нулевой» код 00...0, т. е. признак дефектности соответствующего модуля l. В регистрах

7 исправных модулей 1 записываются номера этих модулей в двоичном коде (дополнительный код адреса). Для этого регистры 7 устанавливаются в исходное состояние 00...0 с помощью шины установки «нуля» (на чертежах не показана). При подаче управляющих сигналов на соответствующие шины 12 открываются вентили 8, и дополнительный код адреса, поступающий по шинам 10, записывается в соответствующий регистр 7, т. е. осуществляется подготовка выбранного модуля 1 для проверки. В дальнейшем производится проверка выбранного модуля с помощью любых известных тестов. Обращения в выбранный модуль осуществляются в соответствии с дополнительным кодом адреса, записанным в регистр 7 проверяемого модуля 1. При каждом обращении по данному дополнительному коду адреса соответствующая схема 9 фиксирует совпадение кода, поступающего по шинам 10, с кодом, хранящемся в регистре 7, и разрешает обращение через вентили 5 и дешифратор 2 в соответствующий модуль. Если в результате проверки выявляется, что выбранный модуль содержит дефектные элементы, то регистр 7 этого модуля устанавливается в исходное состояние, а тот же дополнительный код адреса переписывается в регистр следующего модуля, и проверка повторяется.

Если этот модуль оказывается исправным, то в регистры 7 следующих по порядку модулей

1 записываются следующие по порядку дополнительные коды адреса (например, в порядке возрастания).

Для того, чтобы дополнительный код адреса 00...0, поступающий по шинам 10, отличался от кода 00...0, записанного в регистрах

7 дефектных модулей, в каждом регистре вводится дополнительный триггер 11, в котором записывается «единица», если данный модуль дефектен, и «нуль» — в противном случае.

«Единичный» выход каждого такого триггера блокирует соответствующую схему 9. Этот же триггер можно использовать для полного выключения питания данного дефектного модуля и остальных триггеров соответствующего регистра.

После выявления всех дефектных модулей и записи дополнительных кодов адреса в регистры исправных модулей устройство может работать в нормальном режиме. В этом случае выборка из устройства и запись в него осуществляется в соответствии с кодом адреса, который поступает в устройство по основным адресным шинам 4 и дополнительным шинам 10. В том модуле, на регистре 7 которого хранится код, совпадающий с дополнительным кодом адреса, на выходе схемы 9 появляется сигнал совпадения, разрешающий обращение в этот модуль. В остальном работа устройства не отличается от работы обычных ЗУ.

Предмет изобретения

1. Запоминающее устройство на интегральных схемах, содержащее накопительные модули, вентили, дешифраторы адреса с основными адресными шинами и управляемые источники питания, о т л и ч а ю щ е е с я тем, что, с целью повышения степени интеграции и надежности устройства, в нем каждый модуль содержит регистр, дополнительные вентили и схему сравнения, причем входы регистра соединены с дополнительными адресными шинами, а дешифратор адреса каждого модуля соединен с основными адресными шинами через вентили, вторые входы которых подсоединены к выходу схемы сравнения, входы которой подключены к дополнительным адресным шинам и выходам соответствующего ей регистра, входы управляемых источников питания подключены к выходам схем сравнения соответствующих модулей.

2. Устройство по п. 1, отличающееся тем, что в нем каждый регистр содержит дополнительный триггер, вход которого подсоединен к вспомогательным адресным шинам, а один из выходов этого триггера подсоединен ко входу управляемого источника питания соответствующего модуля, 470860

Составитель Г. Виталиев

Техред 3. Тараненко

Корректор А. Галахова

Редактор Е. Семанова

Типография, пр. Сапунова, 2

Заказ 1992/11 Изд. М 1446 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5