Преобразователь двоичных посылок в посылки с заданной величиной краевых искажений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п11 470928

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 04.07.73 (21) 1945747/26-9 (51) М. Кл. Н 04l 3/00

Н 031< 13 24 с присоединением заявки №

Совета Министров СССР по Мелам изобретений и открытий (53) УДК 621.391.883.2 (088.8) Опубликовано 15.05.75. Бюллетень № 18

Дата опубликования описания 25.08.75 (72) Авторы изобретения

Ф. Г. Гордон, М. Я. Вертлиб и Л. Х. Нурмухамедов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ПОСЫЛОК

В ПОСЫЛКИ С ЗАДАННОЙ ВЕЛИЧИНОЙ КРАЕВЫХ

ИСКАЖЕНИЙ

ГосУлаРственный комитет (23) Приоритет

Изобретение относится к области радиотехнических измерений и может использоваться, в частности, для измерения исправляющей способности аппаратуры передачи данных, устройств контроля каналов и т. д.

Известны преобразователи двоичных посылок в посылки с заданной величиной краевых искажений, которые имитируют текст с заданной зоной величины краевых искажений.

Недостатком таких устройств является невозможность раздельной регулировки краевых искажений по каждому фронту посылки.

С целью обеспечения независимой установки величины краевых искажений переднего и заднего франтов двоичной посылки в предлагаемом преобразователе каналы выделения задержанных переднего и заднего фронтов содержат блоки задержки переднего и заднего фронтов и схемы «ИЛИ», при этом выходы узла выделения фронтов двоичных посылок подключены к входам блоков выделения задержанных переднего и заднего фронтов и блоков задержки переднего и заднего фронтов каналов, в которых выходы блоков выделения задержанных переднего и заднего фронтов и блоков задержки переднего и заднего фронтов через схемы «ИЛИ» подключены к входам триггера-формирователя, а выходы узла управления подключены к вторым входам блоков выделения задержанных переднего и заднего фронтов и блоков задержки переднего и заднего фронтов каналов.

Задавая коммутирующим узлом величину задержки переднего и заднего фронтов посылок и программируя узлом управления количество искаженных посылок в единицу времени, можно получать на выходе преобразователя двоичные посылки с любой заданной величиной краевых искажений в пределах от 0 до

+-50% длительности элементарной посылки, при независимых смещениях переднего и заднего фронтов.

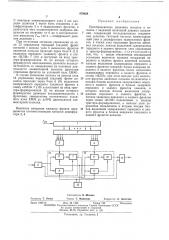

На чертеже приведена структурная схема

15 предлагаемого преобразователя.

Преобразователь содержит делитель 1 тактовой частоты, коммутирующий узел 2, дешифраторы 3 и 4 задержанных фронтов, узел

5 выделения фронтов двоичных посылок, блок

2О 6 выделения задержанного переднего фронта, схему «ИЛИ» 7, блок 8 задержки переднего фронта, блок 9 выделения задержанного заднего фронта, схему «ИЛИ» 10, блок 11 задержки заднего фронта, триггер-формирова25 тель 12, узел 13 управления, канал 14 выделения задержанного переднего фронта, канал

15 выделения задержанного заднего фронта.

Делитель тактовой частоты обеспечивает деление опорной частоты F,„ äo тактовой часЗО тоты, соответствующей скорости передачи.

470928

Предмет изобретения

Составитель Л. Шипова

Техред Т. Миронова Корректор Л, Денисова

Редактор Т. Янова

Заказ 1985/16 Изд. № 1443 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

С помощью коммутирующего узла 2 все разряды делителя 1 могут быть соединены с дешифраторами 3 и 4 задержанных фронтов, в результате чего осуществляется задержка импульсов на величину от 0 до и высокочастотных импульсов Р, где n — коэффициент деления делителя 1.

При отсутствии сигналов управления из узла 13 управления передний (задний) фронт посылки с выхода узла 5 выделения фронтов двоичных посылок проходит через блок 8 (11) задержки переднего (заднего) фронта и схему «ИЛИ» 7 (10) и поступает на вход триггера-формирователя 12, на выходе которого формируется неискаженная двоичная последовательность со смещенными на половину длительности элементарной посылки фронтами (смещение фронтов на условный нуль ХММ).

В случае появления сигнала на выходе узла

13 управления передний (задний) фронт посылки проходит через блок 6 (9) выделения задержанного переднего (заднего) фронта и схему «ИЛИ» 7 (10) и поступает на вход триггера-формирователя 12, на выходе которого формируется двоичная последовательность с фронтами, смещенными относительно условного нуля ХММ до 50/o длительности элементарной посылки.

Величина смещения каждого фронта определяется соответствующим набором дешифратора 3, 4.

Преобразователь двоичных посылок в посылки с заданной величиной краевых искажений, содержащий последовательно соединенные делитель тактовой частоты, коммутирующий узел и дешифраторы задержанных фронтов, а также узел выделения фронтов двоичных посылок, каналы выделения задержанных

10 переднего и заднего фронтов, узел управления и триггер-формирователь, отличающийся тем, что, с целью обеспечения независимой установки величины краевых искажений переднего и заднего фронта двоичной посылки, 15 каналы выделения задержанных переднего и заднего фронтов содержат блоки задержки переднего и заднего фронтов, блоки выделения задержанных переднего и заднего фронтов и схемы «ИЛИ», при этом выходы узла выделе20 ния фронтов двоичных посылок подключены к входам блоков выделения задержанных переднего и заднего фронтов и блоков задержки переднего и заднего фронтов каналов, в которых выходы:блоков выделения задер25 жанных,переднего и заднего фронтов и блоков задержки переднего и заднего фронтов через схемы «ИЛИ» подключены к входам триггера-формирователя, а выходы узла управления подключены к вторым входам бло30 ков выделения задержанных переднего и заднего фронтов и блоков задержки переднего и заднего фронтов каналов.