Устройство синхронизации

Иллюстрации

Показать всеРеферат

< 11 471581

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сава Советских

Социалистических

Рвслублии (61) Дополнительное к авт. свид-ву (22) Заявлено 02.02.73 (21) 1882938/18-24 с присоединением заявки № (23) Приоритет (51) М. Кл. G 061 1/04

Государственный комитет

Совета Министров СССР ио делам изобретений Опубликовано 25.05.75. Бюллетень № 19 (53) УДК 681.326(088.8) и отврытий

Дата опубликования описания 27.08.75 (72) Авторы изобретения

В. С. 3 (71) Заявитель

Институт элект (54) УСТРОЙСТВО СИ НХРО Н ИЗАЦИ И

Изобретение относится к вычислительной технике, в частности к устройствам синхронизации, обеспечивающим заданную последовательность микроопераций.

Известно устройство синхронизации, содержащее регистры на DV-триггерах по числу фаз синхронизации и шины фазовой синхронизации.

Цель изобретения — сокращение оборудования устройства при работе в режиме ожидания.

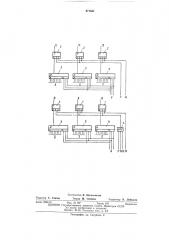

Достигается это тем, что устройство содержит схемы коммутации и схему ИЛИ, выход которой соединен со входами V-триггеров первого регистра, входы V-триггеров второго регистра соединены с входами устройства, входы схемы ИЛИ соединены с выходами триггеров второго регистр а, входы С-триггеров первого и второго регистров соединены с шинами второй и первой фазы синхронизации соответственно, входы D-триггеров соединены с выходами схем коммутации, первые группы входов которых соединены с группами входов устройства, вторые группы входов схем коммутации одного регистра соединены с выходами триггеров другого регистра. На чертеже приведена схема устройства синхронизации.

Устройство синхронизации содержит триггеры 1 первого регистра, триггеры 2 второго регистра, схемы коммутации 3, схему ИЛИ 4, первые группы входов 5, вторые группы входов 6, входную шину 7, выходные шины 8 — 10 триггеров 1, выходные шины 11 — 13 триггеров

5 2, шины первой фазы синхронизации 14 и шины второй фазы синхронизации 15.

Устройство синхронизации работает следующим образом.

Триггеры 1 первого регистра предназначе10 ны для запоминания состояния устройства синхронизации в нечетные такты его работы; триггеры 2 второго регистра — для запоминания состояния устройства синхронизации в четные такты его работы.

15 Схемы коммутации 3 предназначены для выработки сигналов, определяющих следующее состояние устройства синхронизации. Схема ИЛИ 4 предназначена для выработки сигнала, запрещающего изменения состояния

20 первого регистра, когда необходимо обеспечить режим ожидания.

Выбранное число триггеров (по три в каждом регистре), обеспечивающее шестнадцать различных состояний устройства синхрониза25 ции и соответственно столько же различных сигналов на его выходе, является достаточным для описания принципа построения устройства синхронизации, но пе ограничивает возможности его построения с любым числом состоя30 ний, т, е. с любым числом триггеров в каж471581 дом регистре. Соответственно с изменением числа триггеров будет меняться и число схем коммутации 3, и число входов в первой и второй группах входов этих схем коммутации.

Число входов во второй группе 6 входов каждой схемы коммутации 3 может быть любым, например и, тогда число входов в первой группе входов 5 у данной схемы коммутации 3 будет 2". Окончательная конфигурация устройства синхронизации определяется при конкретном задании, причем режимы ожидания можно реализовать как на первом, так и на втором регистрах. Если режим ожидания реализуется и на втором регистре, то в устройство нужно ввести вторую схему ИЛИ и выход ее подключить к входной шине 7. Благодаря описанным связям осуществляется такой принцип работы устройства, что код, например, на выходных шинах 11 —:13 триггеров

2 второго регистра, характеризующий состояние устройства синхронизации в данный момент времени, подается одновременно на вторую группу входов 6 всех схем коммутации 3 первого регистра. При этом, сигналы на входах второй группы входов 6 схем коммутации 3 в зависимости от подаваемого на них кода пропускают на выход каждой схемы код одного из логических условий, подаваемых на первую группу входов 5.

На выходах схем коммутации 3 первого регистра в соответствии с логическими условиями вырабатывается код следующего состояния устройства синхронизации, который запоминается в первом регистре в момент прихода сигнала синхронизации по шине 15. В свою очередь код с выходных шин 8 —:10 триггеров

1 первого регистра одновременно подается на вторую группу входов 6 всех схем коммутации 3 второго регистра. На выходах этих схем коммутации в соответствии с сигналами на входах первой группы входов 5 вырабатывается код следующего состояния устройства, который запоминается во втором регистре в момент прихода сигнала синхронизации по шине 14. Если же на первую группу входов 5 схем коммутации 3 второго регистра не поступили логические условия, которые определяют следующее состояние устройства синхронизации, то на выходах этих схем коммутации 3 вырабатываются нулевые сигналы, которые в момент поступления сигнала по шине 14 записывают в триггеры 2 второго регистра нули. Полностью нулевой код на выходах 11 —:13 второго регистра является нерабочим для этого регистра и используется для выработки схемой ИЛИ 4 сигнала, запрещающего изменение состояния первого регистра.

Таким образом код, установленный в момент поступления сигнала по шине 15 в первом регистре, будет храниться сколько угодно до тех пор, пока не поступят на первую группу 5 входов схем коммутации 3 второго регистра логические условия, необходимые для перевода устройства синхронизации в следующее состояние. Любой ненулевой код на выходах

15 11 †: 13 второго регистра, поступая на схему

ИЛИ 4, вырабатывает сигнал, разрешающий изменение состояния первого регистра.

Такой способ организации режима ожидания требует всего лишь одного нерабочего со20 стояния устройства синхронизации для реализации любого числа состояний, в которых необходим режим ожиданий.

Описанная структура и принцип действия устройства синхронизации позволяют кодиро25 вать состояние устройства любым типом кода: неизбыточным, кодом с постоянными весами, составным кодом и т. д., а также позволяет уменьшить аппаратурные затраты на построение устройства синхронизации.

Предмет изобретения

Устройство синхронизации, содержащее регистры на DV-триггерах по числу фаз синхронизации и шины фазовой синхронизации, от35 личающееся тем, что, с целью сокращения оборудования устройства при работе в режиме ожидания, оно содержит схемы коммутации и схему ИЛИ, выход которой соединен с входами V-триггеров первого регистра, 40 входы V-триггеров второго регистра соединены с входами устройства, входы схемы ИЛИ соединены с выходами триггеров второго регистра, входы С-триггеров первого и второго регистров соединены с шинами второй и пер45 вой фазы синхронизации соответственно, входы D-триггеров соединены с выходами схем коммутации, первые группы входов которых соединены с группами входов устройства, а вторые группы входов схем коммутации одно50 го регистра соединены с выходами триггеров другого регистр а.

471581

7 14 б 11 Ю!3 15

Составитель Ф. Шагиахметов

Техред М. Семенов Корректор Н. Лебедева

Редактор Е, Гончар

Типография, пр. Сапунова, 2

Заказ 2324/12 Изд. № 737 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5