Реле времени

Иллюстрации

Показать всеРеферат

О П И С Л Й=М- Е

ИЗОБРЕТЕНИЯ

<и> 47I 624

Со1оз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 28.06.72 (21) 1802240/26-21 (51) М. Kë. Н Olh 47/18

Н 03k 3/40 с присоединением заявки—

Государственный комитет

Совета Министров СССР ао делам изобретений н открытий (23) Приоритет—

Опубликовало 25.05.75. Бюллетень ¹ 19

Дата опубликования описания 17.11.75 (53) УДК 621.373.52 (088.8) (72) Авторы изобретения

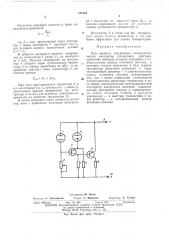

Н. С. Лидореико, А. P. Велиев и В. В. Соболь (71) Заявитель (54) РЕЛЕ ВРЕМЕНИ электрод «склад» подключен к базе транзистора 2;.1орогового усилителя и через токозадающий резистор 8 — к положительному полюсу источника питания.

Электрохимический интегратор дискретного действия 4 подсоединен электродом

«склад» к отрицательному полюсу источника питания, а «рабочим» электродом — к эмиттеру транзистора 2 и через резистор 5 — к положительному полюсу источника питания.

В схеме реле времени применены также транзистор б и резисторы 7, 8. И сточник питания подключается к клеммам 9, 10.

Реле времени работает следующим обра15 зом. .Время выдержки 11 в схеме получается меньше расчетного времени 12 на величину

Ж. При этом с «рабочего» электрода интегратора 1 недос1,пмается заряд

ЛЯ = Яисх Q1

12 11

Изобретение от1осится к радиотехнике и может быть использовано в устройствах автоматики си,измерительной техники.

Известное реле времени содержит электрохимический интегратор дискретного действия, «рабочий» электрод которого подключен ,к отрицательному полюсу .источника питания, а электрод «склад» подключен к базе транзистора порогового усилителя и через токозадающий резистор — к положительному полюсу источника питания.

Однако известное устройство обладает низкой стабильностью отрабатываемых временных интервалов.

Целью изобретения является повышение стабильности отрабатываемых временных интервалов.

Для этого введен дополнительный электрохимический интегратор дискретного действия, подсоединенный электродом «склад» к отрицательному полюсу источника питания, а «рабочим» электродом — к эмиттеру транзистора и через резистор — к положительному полюсу источника 1питания.

На чертеже приведена принципиальная электрическая схема реле времени.

Реле времени содержит электрохимический интегратор дискретного действия 1, «рабочий» электрод которого подключен к отрицательному полюсу источника литания, а где Q„„. — исходный заряд рабочего электрода;

Q1 — заряд, снимаемый за время t1, Таким образом, вместо ожидаемой выдержки времени t> получается время t1, и погрешность реле времени определяется как

47! 624 ра 1 полностью не сниимется заряд Q,-, и падение напряжения на нем не достигнет уровня срабатыванпя транзистора 2.

Интегратор 4 в схеме как бы контроли.рует режим отсе гки !знтегратора 1, что наиболее эффективно при низких температурах.

Реле времени, содержащее электрохимический интегратор дискретного действия, «рабочий» электрод которого подключен к отрицательному полюсу источника питания, а электрод «склад» подключен к базе первого транзистора порогового усилителя и через токозадающий резистор — к положительному полюсу источника питания, отличающееся тем, что, с целью повышения стабильности отрабатываемых временных интервалов, в него введен дополнительный электрохимический интегратор дискретного действия, подсоединенный электродом «склад» к отрицательно»у полюсу источника пита ния, а «рабочим» электродом — к эмиттеру транзистора и через резистор — к положительному полюсу источника питания. /эб — 1 + 220

Составитель Ю. Еркин

Техред Т. Миронова

Корректор В. Гутман

Редактор А. Зиньковский

Заказ 999/1421 Изд. ¹ 850

ЦНИИПИ Государственного комитета по делам изобретений и

Москва, 5К-35, Раушская

Тип. Харьк, фил. пред. «Патент»

Расчетная выдержка времени 1, будет определяться формулой

Яисх

« I 1

1 где I! — ток, протекающий через интегратор 1. Через интегратор 4 протекает ток Iz, для которого должно выполняться условие

12 ++ I! °

В процессе выдержки времени напряжение на интеграторе/ равно U,, на интеграторе 4 AU . Падение напряжения на интеграторе 4 смещает порог срабатывания транзистора 2 в сторону увеличения на ЛУ, и напряжение эмиттер — база транзистора 2 становится равным

При этом приоткрывается транзистор 2, и его эзгиттерный ток I„ñóììèðóÿ "b c током 1з, увеличивает падение напряжения на интеграторе 4 на ЬУ, (на величину изменения напряжения на эмиттере транзистора 2).

В таком состоянии схема находится до тех пор, пока с «рабочего» электрода интегратоПредмет изобретения

Тираж 833 Подписное

Совета Министров СССР открытий наб., д. 4/5