Устройство обнаружения адресного кода

Иллюстрации

Показать всеРеферат

!

ОПИСАНИЕ

ИЗОБРЕТЕ Н И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i > 47I675

Союз Фоеетска

Социалистических

Республик (61) Дополниетльное к авт. свид-ву (22) Заявлено 05.05.72 (21) 1781404/26-9 (51) М. Кл. Н 041 3/08

Н 04I 27/26 с присоединением заявки №

Государственный комитет

Совета Министров СССР ао аелам изебретеиий и открытий (23) Приоритет

Опубликовано 25.05.75. Бюллетень № 19

Дата опубликования описания 02.09.75 (53) УДК 621.376.3 (088,8) (72) Авторы изобретения

М. В. Черняков и М. С. Ярлыков (71) Заявитель (54) УСТРОЙСТВО ОБНАРУЖЕНИЯ АДРЕСНОГО КОДА

Изобретение относится к телефонии, в частности является составной частью приемника асинхронно-адресной системы связи с частотно- временным кодированием.

Известно устройство обнаружения адресного кода, состоящее из и каналов, каждый из которых содержит последовательно соединенные перемножитель, управляемый гетеродином опорного сигнала, интегратор, детектор огибающей и пороговый блок, к управляющему входу которого подключен блок формирования порога срабатывания.

В известном устройстве из-за наличия внутрисистемных помех искажаются полезные сигналы, что ухудшает нормальную работу приемника асинхронно-адресной системы связи с частотно-временным кодированием, и, в частности, работу устройства обнаружения адресного кода.

Цель изобретения — повышение помехоустойчивости устройства.

Это достигается тем, что между входом перемножителя и дополнительным входом блока формирования порога срабатыва ния включены последовательно соединенные измеритель интервала перекрытия полезного и мешающего импульсов, к управляющему входу которого подключен дополнительный выход гетеродина опорного сигнала, и формирователь управляющего напряжения.

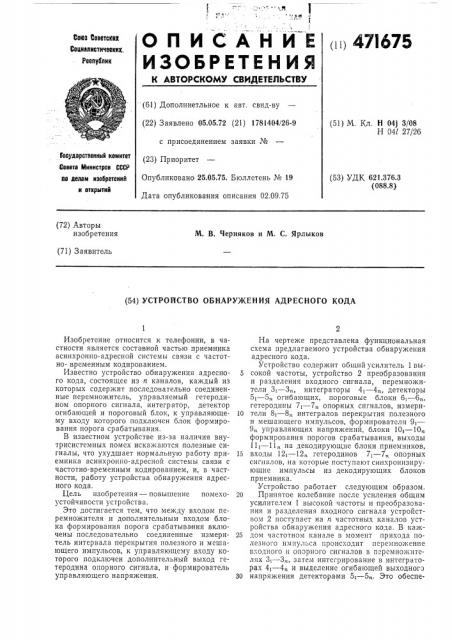

На чертеже представлена функциональная схема предлагаемого устройства обнаружения адресного кода.

Устройство содержит общий усилитель 1 вы5 сокой частоты, устройство 2 преобразования и разделения входного сигнала, перемножители 31 — 3„, интеграторы 4 — 4, детекторы

5 — 5„огибающих, пороговые блоки 61 — 6, гетеродины 71 — 7„опорных сигналов, измери10 тели 8> — 8„интегралов перекрытия полезного и мешающего импульсов, формирователи 9> ——

9„управляющих напряжений, блоки 10,— 10„ формирования порогов срабатывания, выходы

11> — 11„на декодирующпе блоки приемников, 15 входы 12> — 12„> eTe1>o >IHo 7> — 7„опорных сигналов, на которые поступают синхронизирующие импульсы из декодирующих блоков приемника.

Устройство работает следующим образом.

20 Принятое колебание после усиления общим усилителем 1 высокой частоты и преобразования и разделения входного сигнала устройством 2 поступает íà и частотных каналов устройства обнару>кения адресного кода. В каж25 дом частотном канале в момент прихода полезного импульса происходит перемно>кение входного и опорного сигналов в перемно>кителях 3 — 3„, затем интегрирование в интеграторах 4i — 4„и выделение огибающей выходного

Зо напряжения детекторами 51 — 5 . Это обеспе471675

Пер5ый частотио и какал а иа.:r7èãþèû тюкал

Составитель С, Лукннскаи

Редактор А, Батыгин

ЦНИИПИ Заказ 2005/7 Изд. № 729 Тираж 740 Подписное

Типографии, пр, Сапунова, 2 чивается тем, что гетеродины 71 — 7„опорных сигналов открываются стробирущим импульсом из декодирующего устройства приемника только на время прихода полезного сигнала.

Напряжение огибающей поступает на пороговые блоки 6 — 6„и при наличии полезного импульса должно превысить порог срабатывания, фиксируя его наличие.

При подавлении полезного импульса мешающим, напряжение огибающей уменьшается и может оказаться ниже порога срабатывания, в результате чего произойдет пропадание полезного импульса. Чтобы не допустить этого, в каждом канале, предусмотрена регулировка порога срабатывания, состоящая из последовательно соединенных измерителя 81 — 8„интервалов перекрытия полезного и мешающего импульсов и формирователя 9> — 9„управляющего напряжения, воздействующих на блоки

10 — 10 формирования порогов срабатывания.

В результате при подавлении полезного импульса импульсом мешающих одновременно с уменьшением напряжения огибающей уменьшается и порог срабатывания, что позволяет фиксировать наличие подавленного рабочего импульса.

5 Предмет изобретения

Устройство обнаружения адресного кода, состоящее из и каналов, каждый из которых содержит последовательно соединенные nepeI0 множитель, управляемый гетеродином опорного сигнала, интегратор, детектор огибающей и пороговый блок, к управляющему входу которого подключен блок формирования порога срабатывания, о т л и ч а ю щ е е с я тем, что, 15 с целью повышения помехоустойчивости, между входом перемножителя и дополнительным входом блока формирования порога срабатывания включены последовательно соединенные измеритель интервала перекрытия полез20 ного и мешающего импульсов, к управляющему входу которого подключен дополнительный выход гетеродина опорного сигнала, и формирователь управляющего напряжения.