Транзисторное ключевое устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

" 47234I

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 02.01.74 (21) !985372/24-7 с присоединением заявки №вЂ” (23) Приоритет (51) М. Кл. G 05f 1/56

Н 02m 3/14

Н 031с 17/60

Государственный комитет

Совета Министров СССР по делам изаоретений н открытий

Otter()лнковано 30.05.75

Вюллетень ¹ 20 (53) УДК 621.316.722.1 (088.8) Дата опубликования описания 20.01.76 (72) Авторы изобретения

В. П. Миловзоров, Н. И. Дуплин, A. К. Мусолин и Ю. В. Зайцев

Рязанский радиотехнический институт (71) Заявитель (54) ТРАНЗИСТОРНОЕ КЛЮЧЕВОЕ УСТРОЙСТВО

Изобретение относится к области силовой преобразовательной техники и может быть использовано в транзисторных стабилизаторах и преобразователях постоянного напряжения.

Известно транзисторное ключевое устройство, содержащее последовательную цепь из ключевого транзистора с задерживающим дросселем.

Недостатком известного устройства является наличие динамических потерь в ключевом транзисторе при его выключении и задерживающего дросселя, рассчитанного на полный ток нагрузки. Эти недостатки отрицательно сказываются на весогабаритных и энергетических показателях устройства.

Целью изобретения является уменьшение динамических потерь в ключевом транзисторе габаритов задерживающего дросселя.

Для этого в предлагаемом устройстве основной ключевой транзистор с последовательно соединенным задерживающим дросселем шунтирован дополнительным ключевым транзистором, сигнал управления которого отстает по фазе от основного, и цепочкой из последовательного соединения конденсатора, шунтированного разрядным резистором, и маломощного транзистора, сигнал управления которого отстает по фазе от дополнительного.

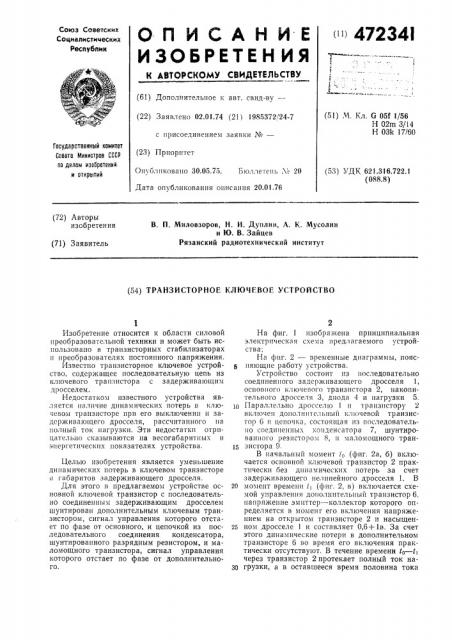

На фиг. 1 изображена принципиальная электр ческая схема предлагаемого устройства;

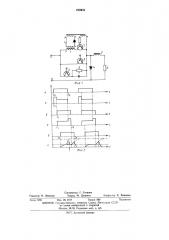

На фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство состоит пз последовательно соединенного задерживающего дросселя 1, основного ключевого транзистора 2, накопительного дросселя 3, диода 4 и нагрузки 5. о Параллельно дросселю н транзистору 2 включен дополннтсльный ключевой транзистор 6 н цепочка, состоящая из последовательно соединенных конденсатора 7, шунтированного резистором 8, и маломощного транзистора 9.

В начальный момент ttt (фиг. 2а, б) включается основной ключевой транзистор 2 практически без динамических потерь за счет задерживающего нелинейного дросселя 1. В

20 момент времени tt (фпг. 2, в) включается схемой управления доно,пгительпый транзистор 6, напряжение эмиттер — коллектор которого определяется в момент его включения напряжением на открытом транзисторе 2 и насыщен25 ном дросселе 1 и составляет 0,6+1в. За счет этого динамические потери в дополнительном транзисторе 6 во время его включения практически отсутствуют. В течение времени to — tt через транзистор 2 протекает полный ток наЗО грузки, а в оставшееся время половина тока

3 нагрузки, Вторая половина тока нагрузки с момента ti протекает по транзистору 6 (фиг. 2 г).

В момент времени 4 (фиг. 2д) включается схемой управления маломощный транзистор 9 и начинается заряд конденсатора 7 (фиг. 2, е) до величины напряжения эмиттерколлектор У„,„открытого транзистора 6. Напряжение насыщения транзистора 9 мало изза небольшого тока заряда конденсатора 7.

В момент 1 схемой управления закрывается основной транзистор 2 (фиг. 2 а, б), динамические потери которого па выключение практически отсутствуют из-за наличия напряжения насыщения транзистора 6. По транзистору 6 протекает с момента времени (фиг. 2, r) полный ток нагрузки. В момент времени t4 (фиг. 2, r) схемой управления закрывается дополнительный транзистор 6, динамические потери которого ITB выключение также отсутствуют пз-за наличия напряжения на конденсаторе 7. С момента времени 4 до

4 (фиг. 2, е) конденсатор 7 дозаряжается по цепи: транзистор 9, источник питания, нагрузка 5, дроссель 3. В момент времени (фиг. 2, д) закрывается схемой управления маломощный транзистор 9 и конденсатор 7

472341

4 разряжается на резистор 8. При открытии основного транзистора 2 цикл коммутации повторяется.

Сопротивление резистора 8 выбирается из

5 условия протекания небольшого тока открытого маломощного транзистора 9. Динамические потери транзистора 9 при его включении отсутствуют, а при включении незначительны из-за малого изменения напряжения па копip денсаторе 7.

Ввиду протекания половины тока агрузки через дроссель 1 уменьшается его расчетная мощность, а следовательно, и габариты.

Предмет изобретения

Транзисторное ключевое устройство, содержащее последовательную цепь из ключевого транзистора с задерживающим дроссе2р лем, отличающееся тем, что, с целью уменьшения динамических потерь и габаритов, указанная последовательная цепь шунтирована дополнительным ключевым транзистором и дополнительной последовательной цепью, состоящей из маломощного транзистора и параллельно соединенных резистора и конденсатора.

472341

Рiг ) Составитель Г. Стоянов

Техред М. Дворина

Редактор В. Левятов

Корректор Е. Рожкова

Заказ 6391 Изд. № 1517 Тираж 869

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Подписное

МОТ, Загорский филиал