Стабилизатор напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬРЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (II) 472342

Союз Советских

Социалистических

Республик (61) Дополнительное,к авт. свид-ву (22) Заявлено 12.07.73 (21) 1940987/24-7 с присоединением заявки № (23) Приоритет

Опубликовано 30.05.75. Бюллетень ¹ 20

Дата опубликования описания 16.09.75 (51) М. Кл. 4 05f 1. 58

Государственный катеитет

Совета й1инистров СССР

{53) > Д1с, 621 316, (22 1 (088,8) ло делам изобретений и открытий (72) Авторы изобретения

В. И. Ковальков и Ю, К. Филипский (71) Заявитель

Одесский политехнический институт (54) СТАБ ИЛ ИЗАТО Р НАН РЯ)КЕН ИЯ

Изобретение может использоваться в качестве лабораторных источников питания при отладке, настройке или испытаниях различных полупроводниковых схем, а также для питания радиоэлектронной аппаратуры.

Известны стабилизаторы напряжения с ограничением тока нагрузки, содержащие по крайней мере один канал с входным балансным каскадом, коллектор управляющего транзистора которого через согласующий усилитель подключен к регулирующему транзистору, дополнительный токоизмерительный балансный каскад и опорные стабилитроны входного и токоизмерительного каскадов.

Известные схемы стабилизаторов с ограничением тока нагрузки «Ie позволяют регулировать ток ограничения в широких пределах, обеспечивая защиту только стабилизатора, но не нагрузки; не допускают регулировки выходного напряжения стабилизатора либо имеют связь тока ограничения с величиной выходного напряжения; имеют низкую температурную стабильность максимально допустимого тока нагрузки 1„„,,-, при котором еще сохраняются характеристики стабилизатора.

В двухканальных стабилизаторах применение известных схем защиты либо не обеспечивает одновременного отключения обоих каналов при коротких замыканиях»а выходе одного из них, либо не допускает пораздельного регулирования ограничиваемого тока каналов.

Цель предлагаемого изобретения заключается в устранении перечисленных выше недо5 статков.

В предлагаемом стабилизаторе последовательного типа эта цель достигается тем, что коллектор одного транзистора токоизмерительного балансного каскада подключен к

10 эмиттеру управляющего транзистора, а коллектор другого транзистора — к опорному стабилитрону входного балансного каскада стабилизатора, коллектор другого транзистора которого подключен к опорному стабнли15 трону токоизмерительного бал ансного каскада. Причем в многоканальной структуре стабилизатора коллектор соответствующего транзистора токоизмерительного баланспого каскада одного канала подключен к опорному

20 стабилитрону входного балансного каскада противоположного канала.

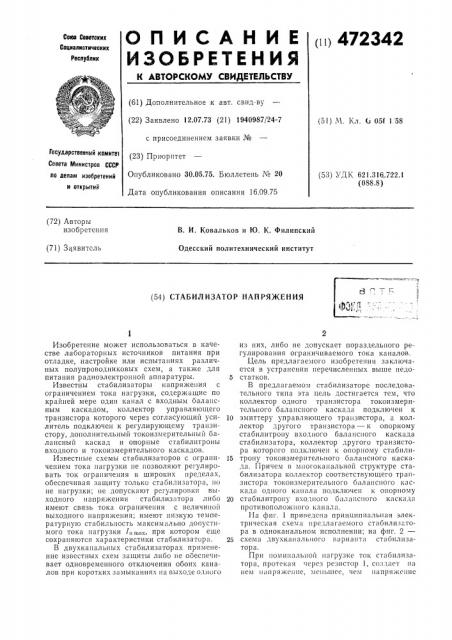

Иа фиг. 1 приведена принципиальная электрическая схема предлагаемого стабилизатора в одноканальном исполнении; на фиг. 2—

25 схема двухканального варианта стабилизатора.

При номинальной нагрузке ток стабилизатора, протекая через резистор 1, создает па нем II IïðIIженпе, меньшее, чем напряжение

472342 на стабилитроне 2. Транзистор 3 закрыт и коллекторный ток транзистора 4, определяемый резистором 5 балансного токоизмерительного каскада 6, протекает через источник опорного напряжения — стабилитрон 7.

В балансной схеме управления 8 открыты оба транзистора 9 и 10. Коллекторный ток транзистора 9 управляет регулирующим элементом 11, а коллекторный ток транзистора

10, зависящий от величины резистора 12, определяет рабочую точку стабилитрона 2.

Таким образом, образуется глубокая отрицательная обратная связь, охватывающая оба балансных каскада и стабилизирующая их режим.

Сопротивления коллекторных переходов транзисторов 4, 10 во много раз больше динамических сопротивлений стабилитронов 2, 7.

Благодаря этому обеспечивается высокий коэффициент стабилизации опорных источников, более чем на два порядка превышающий коэффициент стабилизации обычного параметрического стабилизатора с балапсным сопротивлением, что положительно сказывается на характеристике всего стабилизатора напряжения: повышается коэффициент стабилизации, снижаются уровень пульсаций выходного напряжения и выходное сопротивление.

Когда ток нагрузки превышает максимально допустимое значение, напряжение на резисторе 1 становится больше опорного напряжения стабилитрона 2 и транзистор 3 открывается. Часть тока балансной схемы управления 8 ответвляется в коллекторную цепь транзистора 3. Коллекторные токи транзисторов 9, 10 уменьшаются, что приводит к подзапиранию регулирующего элемента 11 и уменьшению выходного напряжения. В дальнейшем коллекторный ток транзистора 11 уменьшается настолько, что рабочая точка стабилитрона 2 переходит на пологий участок.

Уменьшение опорного напряжения на стабилитроне 4 приводит к еще большему открыванию транзистора 3 и запиранию транзистора 4. Одновременно уменьшается ток через стабилитрон 7 и падает его опорное напряжение, что, в свою очередь, приводит к уменьшению коллекторных токов тра нзисторов 9, 10. После устранения короткого замыкания схема автоматически возвращается в исходное положение.

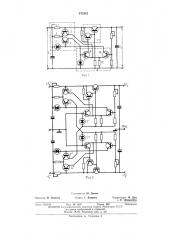

На фиг. 2 представлена схема стабилизатора с двумя идентичными разнополярными каналами. Опорные источники входных каскадов имеют полярность папря>кения, ооратную выходному папря>кению канала, что по:1во5

55 ляет регулировать выходные напряжения стабилизатора вплоть до нуля. В отличие от схемы на фиг. 1 коллекторы соответствующих транзисторов обоих каналов 4, 4" токоизмеряющих балансных каскадов на транзисторах

3, 3"; 4, 4" подключены к опорным стабилизаторам входных каскадов противоположных каналов 7" и 7 соответственно. Таким образом, взаимной обратной связью охватываются все четыре балансных каскада стабилизатора.

Это позволяет несмотря на то, что в стабилизаторе обеспечивается регулировка максимального нагрузочного тока каждого канала в отдельности и различие в величинах этих токов, осуществить одновременное отключение каналов (снижение выходного напряжения до нуля) при перегрузке любого из них.

Схема работает аналогично одноканальной.

Управление выходным напряжением канала, не подвергшегося перегрузке, осуществляется изменением опорного напряжения на стабилитронах 7, 7" (коллекторных токов транзисторов 4", 4 ) .

Предмет изобретения

1. Стабилизатор напряжения с ограничением тока нагрузки, содержащий по крайней мере один канал с входным балансным каскадом, коллектор управляющего транзистора которого через согласующий усилитель подключен к регулирующему транзистору, дополнительный токоизмерительный балансный каскад и опорные стабилитроны входного и токоизмерительного каскадов, о тл и ч а ющ и и ся тем, что, с целью расширения пределов регулирования тока срабатывания и выходного напряжения стабилизатора, а также повышения стабильности их величин, коллектор одного транзистора токоизмерительного балансного каскада подключен к эмиттеру управляющего транзистора, а коллектор другого транзистора — к опорному стабилитрону входного балансного каскада стабилизатора, коллектор другого транзистора которого подключен к опорному стабилитрону токоизмерительного балансного каскада.

2. Стабилизатор напряжения по п. 1, отл и ч а ю шийся тем, что, с целью расширения функциональных возможностей и повышения надежности, в многоканальной структуре стабилизатора коллектор соответствуюшего транзистора токоизмерительного балансного каскада одного канала подключе1! к опорному стабилитрону входного бала!1с!юга

КаСКа, 1 <1 iipo????????1!??????>1(!!(1! 0 К<1 па:!11.

472342

Фиг 7

"Е

Составитель Ю. Дычко

Техред Г. Дворина

Редак1ор В. Левятов

Корректоры: В. Дод и Е. Давыдкина

Типография, пр Сапунова, 2

Заказ 22!3/10 Изд. № 1497 Тираж 869 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Рау.шская наб., д. 4/5