Распредилитель сигналов

Иллюстрации

Показать всеРеферат

«» 472472

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

=оюз Советских

Социалистических

Республик (61) Допол интел ьпое к а вт. свпд-ву —— (22) Заявлено 29.05.72 (21) 1792978. 26-21 с присоедш|енпем заявки ¹â€” (32) Прпорптст ——

Оплпиковано 30.05.75. Вюллстснь,Л 20 (5!) М. Ел. H 041 13/14

Н 03k 17/62

Государственный комитет

Совета Министров СССР

flo делам иэооретений и открытии (53) х ДК 021.374(088.8) Дата опубликования описания 23.12.75 (72) Авloj) изобретения т1. А. Грехнев (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ СИГНАЛОВ

Изобретение относится к вычислительной технике и предназначено для распределения сигналов последовательно по т выходным шинам.

Известен распределитель сигналов, содержащий в ячейке каждого разряда элемент памяти с тремя устойчивыми состояниями и элементы «И — НЕ/ИЛИ вЂ” НЕ».

Цель изобретения — уменьшение количества элементов.

Это достигается тем, что в предлагаемом распределителе сигналов в ячейке каждого разряда выход второго плеча элемента памяти соединен с входом первого элемента

«И — НЕ/ИЛИ вЂ” HE», выход которого соединен с входом второго элемента «И†HE/

ИЛИ вЂ” НЕ», выход второго элемента соединен с входом установки элемента памяти в третье состояние, с входом первого элемента

«И — НЕ/ИЛИ вЂ” НЕ», с входом четвертого элемента «И вЂ” HE/ИЛИ вЂ” НЕ», выход третьего плеча элемента памяти соединен с входом третьего элемента «И вЂ” НЕ/ИЛИ вЂ” НЕ», выход которого соединен с входом четвертого элемента

«И — НЕ/ИЛИ вЂ” HE», выход четвертого элемента соединен с входом установки элемента памяти в первое состояние, с входом третьего элемента «И вЂ” НЕ/ИЛИ вЂ” НЕ», а также с входом второго элемента «И вЂ” НЕ/ИЛИ вЂ” НЕ» последующего разряда и с входом установки элемента памяти последующе -о разряда во второе состояние, причем тактирующий сигнал подан на входы второго и четвертого элементов «И вЂ” HE/ÈËÈ вЂ” НЕ».

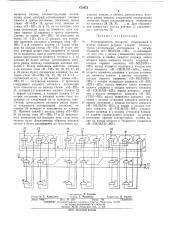

5 На чертеже изображена схема предлагаемого распределителя сигналов с числом ячеек, равным трем (число ячеек может быть любым).

Схемы «И — HE» 1 — 9 образуют элементы

10 памяти 10, 11 и 12 с тремя устойчивыми состояниями. Схемы «И — НЕ» 13, 14 и 15 являются первыми схемами «И вЂ” НЕ», схемы

16, 17 и 18 — вторыми, схемы 19, 20 и 21— третьими, схемы 22, 23 и 24 — четвертыми

15 схемами «И вЂ” НЕ». В начальный момент времени элемент памяти 12 устанавливается во второе состояние, остальные элементы памяти находятся в первом состоянии. В этом случае на выходах схем «И вЂ” IE» 1, 2, 4, 5, 7 и

2О 9 — логическая единица, на выходах схем

«И — НЕ» 3, 6 и 8 — логический нуль. Поскольку в начальный момент времени входной сигнал т, подаваемый на клемму 25, отсутствует, т. е. равен нулю, на выходах схем

25 «И — HE» 22, 16, 23, 17, 24 и 18 — логическая единица. Следовательно, на выходах схем «И вЂ” HE» 19, 13, 20, 14 и 21 — логический нуль, а на выходе схемы «И — НЕ» 15— логическая единица. С приходом входного

30 сигнала т на выходе схемы «И — НЕ» 18 по472472

Предмет изобретения т17 29 Z8

52

Составитель В. Грехнев

Тсхред Т. Миронова

Корректор Л. Орлова

Редактор Е. Караулова

Заказ 5496 Изд. № 1507 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

МОТ, Загорский филиал

3 является сигнал, соответствующий логическому нулю, который устанавливает элемент памяти в третье состояние; поскольку выход схемы «И — НЕ» 18, кроме того, заведен на схемы «И — НЕ» 24 и 15, то на выходах этих схем логический нуль не появится, хотя элемент памяти 12 перешел в третье состояние.

Сигнал со схемы «И — НЕ» 18 поступает на схему «И- — НЕ» 24 и 15 раньше, чем изменение значения сигналов с выходов схем «И—

НЕ» 7 и 8 элемента памяти 12. Таким образом, на выходе схемы «И — НЕ» 18 будет сигнал, который может быть направлен по одной из m выходных шин и длительность которого равна длительности входного сигнала т, а на клемме 26 будет сигнал, длительность которого равна периоду следования входных сигналов т. После окончания действия сигнала т на выходах схем «И вЂ” НЕ» 22, 16, 23, 17, 24 и 18 снова будет логическая единица, на выходах схем «И вЂ” НЕ» 19, 13, 20, 14 и 15— логический нуль, а на выходе схемы «И—

НЕ» 21 — логическая единица. С приходом следующего входного сигнала т логический нуль появляется на выходе схемы «И — НЕ»

24, который устанавливает элемент памяти 12 в первое состояние, а элемент памяти 11 во второе состояние и который может быть направлен по следующей из и выходных шин.

Сигнал, длительность которого равна периоду следования тактирующих сигналов, на клемме 26 исчезает и появляется на клемме

27. Наличие связей с выхода схемы «И — НЕ»

24 на входы схем «И вЂ” HE» 17 и 21 препятствует появлению на выходах этих схем логического нуля. Аналогичным образом входной сигнал т будет распределен по остальным выходным шинам, а сигнал, длительность которого равна периоду следования тактирующих сигналов, будет последовательно появляться па клеммах 28, 29, 30,..., m, Для образования замкнутого кольца контакт 31 соединяется с контактом 32.

10 Распределитель сигналов, содержащий в ячейке каждого разряда элемент памяти с тремя устойчивыми состояниями и четыре элемента «И вЂ” НЕ/ИЛИ вЂ” НЕ», отличающийся тем, что, с целью уменьшения количества

15 элементов, в ячейке каждого разряда выход второго плеча элемента памяти соединен с входом первого элемента «И вЂ” НЕ/ИЛИ—

IE», выход которого соединен с входом второго элемента «И вЂ” НЕ/ИЛИ вЂ” НЕ», выход

20 второго элемента соединен с входом установки элемента памяти в третье состояние, с входом первого элемента «И вЂ” НЕ/ИЛИ—

НЕ», с входом четвертого элемента «И вЂ” НЕ/

ИЛИ вЂ” НЕ», выход третьего плеча элемента

95 памяти соединен с входом третьего элемента

«И — НЕ/ИЛИ вЂ” НЕ», выход которого соединен с входом четвертого элемента «И вЂ” НЕ/

ИЛИ вЂ” НЕ», выход четвертого элемента соединен с входом установки элемента памяти в

30 первое состояние, с входом третьего элемента

«И — НЕ/ИЛИ вЂ” HE», а также с входом второго элемента «И вЂ” НЕ/ИЛИ вЂ” HE» последующего разряда и с входом установки элемента памяти последующего разряда во второе

35 состояние, причем тактирующий сигнал подан на входы второго и четвертого элементов

«И — HE/ИЛИ вЂ” НЕ».