Матричный осциллограф

Иллюстрации

Показать всеРеферат

ПИСАНИЕ

ИЗОБРЕТЕНИЯ

О р 473I03

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 27.03.74 (21) 2008824/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.06.75. Бюллетень № 21

Дата опубликования описания 03.09.75 (51) M. Кл. G Olr 13/10

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.317.75 (088.8) (72) Автор изобретения

В. В. Сумароков (71) Заявитель (54) МАТРИЧНЫЙ ОСЦИЛЛОГРАФ

Изобретение относится к электроизмерительной технике, может быть использовано для многоканальной индукции сигналов, синхронизации изображения и запоминания однократных сигналов.

Известен матричный осциллограф, содержащий входную цепь, образованную аттенюатором, суммирующим усилителем, компаратором и одновибратором, входом связанным с выходом компаратора, первый вход которого соединен через суммирующий усилитель с выходом аттенюатора, второй вход — с выходом цифро-аналогового преобразователя, входы которого соединены с выходами первого двоичного счетчика, входом связанного с выходом генератора импульсов развертки, выходами— со входами первого дешифратора, выходами соединенного с горизонтальными шинами матрицы экрана, вертикальные шины которой связаны с выходами второго дешифратор а, входы которого подключены к выходам второго двоичного счетчика, и светоэлементы.

Предлагаемый осциллограф отличается от известных тем, что он снабжен дополнительными схемами «И», триггерами, схемой

«ИЛИ» и, по числу входных сигналов, входными цепями, вторые входы компараторов которых подключены к выходу цифро-аналогового преобразователя, выходы одновибраторов — ко входам схемы «ИЛИ», выход которой соединен с первыми входами схем «И» узлов матрицы, вторые и третьи входы которых связаны с шинами, образующими узел, выходы— со вторыми входами триггеров, первые входы которых подключены к предыдущим вертикальным шинам, выходы — к светоэлементам, причем нулевой выход первого дешифратора соединен с первым входом схемы «И» управления, второй инверсный вход которой подключен к последнему выходу второго дешифратора, выход — к счетному входу второго счетчика, вход сброса в нуль которого связан через ключ с выходом схемы «И», включенной в крайний по вертикали и средний по горизонтали узел матрицы.

Такое выполнение устройства позволяет обеспечить многоканальную индикацию си:налов, синхронизацию изображения и возможность запоминания однократных сигналов.

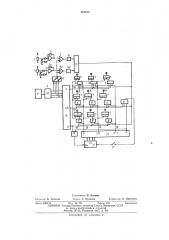

20 Блок-схема устройства приведена на чертеже.

Устройство состоит из входных цепей по числу входных сигналов, каждая из которых образована аттенюатором 1, суммирующим

25 усилителем 2, компаратором 3 и одновибратором 4; схемы «ИЛИ» 5, схем «И» узлов матрицы 6, триггеров 7, светоэлементов 8, генератора импульсов развертки 9, первого двоичного счетчика 10, цифро-аналогового преобра30 зователя 11, первого дешифратора 12, схемы

473103 управления «И» 13, второго двоичного счетчика 14, второго дешифратора 15, схемы «И»

16, включенной в крайний по вертикали и средний по горизонтали узел матрицы, ключа

17, горизонтальных шин 18 и вертикальных шин 19.

Работает устройство следующим образом.

Входные сигналы через аттенюаторы 1 и усилители 2 поступают на первые входы компараторов 3, на вторые входы которых подается опорное ступенчатое напряжение с преобразователя 11. В моменты равенства опорного и входных напряжений на выходах компараторов 3 образуются перепады напряжений, запускающие одновибраторы 4. Короткие выходные импульсы одновибраторов логически складываются в схеме «ИЛИ» 5. Импульсы генератора 9 запускают счетчик 10, комбинации двоичных чисел на выходных шинах которого преобразуются преобразователем

11 в ступенчатое напряжение и возоуждают на выходе дешифратора 12 шину, номер которой соответствует двоичному числу. Импульс, периодически появляющийся на нулевой шине дешифратора, запускает через схему «И» 13 счетчик 14, нагруженный на дешифратор 15.

Дешифратор 15 переключается с состояния

«0» до «п» и останавливается, подав запрещающий сигнал на схему «И» 13, которая не пропускает запускающие импульсы на счетчик 14. Импульс на выходе схемы «ИЛИ» 5, несущий информацию о величинах входных напряжений в момент i-того состояния дешифратора, проходит только ту схему «И» 6 и запускает только тот триггер 7, которые находятся в узле пересечения i-той шины 15 и

j-той шины 12, номер которой пропорционален по величине одному из входных сигналов. При переключении дешифратора 15 в состояние

1+1, зажигаются другие элементы, расположенные в соседнем столбце экрана, характеризующие своей высотой величины входных напряжений и т. д, Таким образом на экране возникает изображение входных напряжений, которое при разомкнутом ключе 17 запомнится осциллографом. Когда замыкается ключ и изображение одного из входных напряжений проходит через среднюю горизонтальную шину экрана, срабатывает схема «И»

16, и ее импульсы сбрасывает в «О» счетчик 14 и дешифратор 15. Тем самым обеспечивается синхронизация изображения, и осциллограф снова выполняет развертку изображения, предварительно погасив предыдущее через сбросовые входы триггеров 7.

Предмет изобретения

Матричный осциллограф, содержащий входную цепь, образованную аттенюатором, суммирующим усилителем, компаратором и одновибратором, входом связанным с выходом компаратора, первый вход которого соединен через суммирующий усилитель с выходом аттенюатора, второй вход — с выходом цифроаналогового преобразователя, входы которого соединены с выходами первого двоичного счетчика, входом связанного с выходом генератора импульсов развертки, выходами — со входами

20 первого дешифратора, выходами соединенного с горизонтальными шинами матрицы экрана, вертикальные шины которой связаны с выходами второго дешифратора, входы которого подключены к выходам второго двоичного счетчика, и светоэлементы, отличающийся тем, что, с целью обеспечения многоканальной индикации сигналов, синхронизации изображения и возможности запоминания однократных сигналов, он снабжен дополЗ0 нительными схемами «И», триггерами, схемой «ИЛИ», и, по числу входных сигналов, входными цепями, вторые входы компараторов которых подключены к выходу цифро-аналогового преобразователя, выходы

35 одновибраторов — ко входам схемы «ИЛИ», выход которой соединен с первыми входами схем «И» узлов матрицы, вторые и третьи входы которых связаны с шинами, образующими узел, выходы — со вторыми входами тригге40 ров, первые входы которых подключены к предыдущим вертикальным шинам, выходы — к светоэлементам, причем нулевой выход первого дешифратора соединен с первым входом схемы «И» управления, второй инверсный

45 вход которой подключен к последнему выходу второго дешифратора, выход — к счетному входу второго счетчика, вход сброса в нуль которого связан через ключ с выходом схемы

«И», включенной в крайний по вертикали и

50 средний по горизонтали узел матрицы, 473103

Составитель В. Лившиц

Текред Т. Курилко

Редактор Б. Федотов

Корректор Л. Брахнина

Типография, пр. Сапунова, 2

Заказ 2008/14 Изд. № 757 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5