Устройство для измерения отклонения частоты от нормального значения

Иллюстрации

Показать всеРеферат

О П И С А Н И E I (») 473ll5

ИЗОБРЕТЕН ИЯ

И ABTGPCIKQA У СВИДЕТЕЛЬСТВУ

Сон>з Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 04.05.73 (21) 1913430/26-21 j (51) М. Кл. G Olr 23/04 с присоединением заявки ¹

Государственный ко»нтет

Совета Министров СССР оо делом изобретений н открытий (32) Приоритет

Опубликовано 05.06.75. Бюллетень № 21

Дата опубликования описания 22.09.75 (53) УДК 621.317.761 (088.8)

1 ! (72) Авторы изобретения

A. A. Килна, Р. Ю. Орлинис и Г, >I. Вейверис

Институт физики и математики AH Литовской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТКЛОНЕНИЯ ЧАСТОТЫ

ОТ НОМИНАЛЬНОГО ЗНАЧЕНИЯ

Изобретение относится к области электроизмерительной техники и может быть использовано при создании устройств для измерения отклонения частоты от номинального значения.

Известны устройства для измерения отклонения частоты от номинального значения, содержащие счетчик импульсов с подключенной к его входу схемой «И», входы которой соединены с генератором эталонных импульсов и триггером, счетным входом, подключенным через схему «ИЛИ», линию задержки, формирователи импульсов и триггер к входной шине. Однако эти устройства не позволяют определить максимальное отклонение частоты за время измерения.

Цель изобретения — определение максимального отклонения частоты за время измерения.

Предлагаемое устройство снабжено регистром, вторым счетчиком, второй линией задержки, третьим формирователем импульсов, третьим и четвертым триггерами, двумя схемами «ИЛИ», второй и третьей схемами «И» и двумя группами схем «И», причем выходы второй схемы «И» через первую группу схем

«И», регистр и вторую группу схем «И>., к вторым входам которой подключены выходы счетчика, а к третьим входам через дешифратор — выходы второго счетчика, соединены с входами схем «ИЛИ», выходы которых через третий триггер подключены к входу второй схемы «И», соединенной по второму входу с входом второго счетчика и черсз дешифратор, третий формирователь — с его выходом, при этом вход третьей схемы «И» подключен к выходу генератора эталонных импульсов, ее выход — к второму входу счет10 чика, а второй вход ее через четвертый триггер соединен с входом второго счетчика и второй линией задержки, выход которой подключен к входам счетчика и к входу третьего триггера.

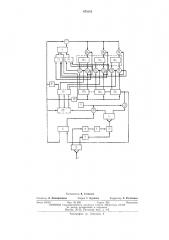

I5 Блок-схема описываемого устройства представлена на чертеже.

Устройство содерж11T входную шипу 1, триггеры 2, 3, 4 и 5, формирователи импульсов

6, " и 8, линии задержек 9 и 10, генератор 11 эт",ëî»íüë импульсов, схемы «ИЛИ» 12, 13 и

14, схс..>ы «И» 15, 16, 17, регистр, состоящий !

;3 разря;Ов 18;, 18., 18, со схемамн «И»

191, 19>, ..., 19„передачи кода из счетчика

25 с разрядами 20., 20, "., 20„, схем «И»

211, 211, ..., 21, v 211, 212, ..., 21,, включенных между выходами разрядов счетчика и регистра, дешифратора 22 и счетчика импульсов 23.

473115

Работает устройство следующим образом.

Триггеры 2 и 4, формирователи импульсов

6 и 7, линия задержки 9 и схема «ИЛИ» 12 служат для определения абсолютного значения отклонения периода входного сигнала.

Импульсы входной исследуемой последовательности опрокидывают триггер 2, перепады напряжения на выходах которого формируются в две импульсные последовательности формирователями импульсов 6 и 7. Одна из них на вход схемы «ИЛИ» 12 поступает непосредственно, а другая — через линию задержки 9, время задержки которой равно номинальному периоду исследуемого сигнала.

Поэтому триггер 4 в единичном состоянии находится в течение времени, равного абсолютному значению отклонения периода от номинального значения. Код отклонения частоты формируется счетчиком с разрядами 20r, 20г, ..., 20„, на вход которого эталонные заполняющие импульсы от генератора 11 поступают через схему «И» 15.

Остальная часть устройства используется для сравнения кода счетчика с кодом регистра, в котором зафиксировано максимальное отклонение периода до данного момента времени. Сравнение кодов счетчика и регистра проводится следующим образом. После определения кода отклонения периода триггер 3 находится в единичном состоянии, так как импульсы со схемы «И» 15 во время счета подаются также и на единичный вход триггера 3. Поэтому импульсы генератора 11 через схему «И» 16 проходят на вход счетчика 23, выходы разрядов которого подключены к дешифратору 22. Дешифратор 22, начиная с младшего разряда, поочередно выбирает все схемы «И» 21ь 21>, ..., 21„и 21r, 21, t

21, выходы которых подключены соответственно к схемам «ИЛИ» 13 и 14.

Схемы «И» 21r, 21, ..., 21„21r, 212 ..., 21, выдают сигнал, когда значения разрядов регистра и счетчика не совпадают, При этом триггер 5 устанавливается в единичное состояние, когда в данном разряде счетчика, выбранном дешифратором 22, находится единица, регистра — ноль, и в нулевое состоя20

45 ние — в противоположном случае. После перебора всех разрядов срабатывает формирователь импульсов 8, который при единичном состоянии триггера 5 (это соответствует коду счетчика, большему кода регистра) производит передачу кода счетчика в регистр.

Тот же импульс формирователя 8 устанавливает счетчик 23 и триггер 3 в исходные состояния и, задержанный линией задержки 10, производит установку нуля разрядов 20r, 20р, 20„основного счетчика. Этим заканчивается один цикл измерения, и в следующем периоде входного сигнала устройство работает аналогичным образом.

Предмет изобретения

Устройство для измерения отклонения частоты от номинального значения, содержащее счетчик импульсов, схему «И», генератор эталонных импульсов, схему «ИЛИ», линию задержки, два формирователя импульсов, дешифратор и два триггера, отличающееся тем, что, с целью определения максимального отклонения частоты за время измерения, оно снабжено регистром, вторым счетчиком, второй линией задержки, третьим формирователем импульсов, третьим и четвертым триггерами, двумя схемами «ИЛИ», второй и третьей схемами «И» и двумя группами схем «И», причем выходы второй схемы «И» через первую группу схем «И», регистр и вторую группу схем «И», к вторым входам которой подключены выходы счетчика, а к третьим входам через дешифратор — выходы второго счетчика, соединены с входами схем

«ИЛИ», выходы которых через третий триггер подключены к входу второй схемы «И», соединенной. по второму входу с входом второго счетчика и через дешифратор, третий формирователь — с его выходом, при этом вход третьей .схемы «И» подключен; к выходу генератора. эталонных импульсов, ее выход— к второму входу счетчика, а второй вход ее через четвертый триггер соединен с входом второго счетчика и второй линией задержки, выход которой подключен к входам счетчика и к входу третьего триггера.

473115

Составитель В. Степанов

Корректор Е. Рогайлина

Редактор Л. жаворонкова

Техред Т. Курилко

Типография, пр. Сапунова, 2

Заказ 2314/1 Изд. ¹ 809 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-35, Раушская наб., д. 4(5