Дискретное логическое устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 473l83

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 22.07.70 (21) 1469017/18-24 (51) М. Кл. б 06f 11/00 с присоединением заявки №

Государственный комитет

Совета Министров СССР па делам изобретений (23) Приоритет

Опубликовано 05.О6.75. Бюллетень № 21

Дата опубликования описания 03.09.75 (53) УДК 621.326(088.8) и открытий (72) Авторы изобретения

Е. Д. Зайденберг и М. Д. Ходырева (71) Заявитель

Г ..:... (54) ДИСКРЕТНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике.

Известны дискретные логические устройства, содержащие функциональные логические блоки и выходные блоки, связи между которыми осуществляются через разъемы.

Недостатком таких устройств является наличие неконтролируемых по обрыву участков схем, содержащих контакты разъемов.

Целью изобретения является повышение надежности контроля дискретных логических устройств.

С этой целью в предложенном устройстве разъемы функциональных логических блоков содержат дополнительные контакты, соединенные перемычками с соответствующими основными контактами, к которым подключены вентильные элементы, причем каждая перемычка включена последовательно в цепь между функциональными и выходным блоком.

На фиг. 1 показан участок схемы предложенного устройства, содержащий распределенную схему «И»; на фиг. 2 — участок схемы, содержащий двухкаскадный усилитель и ответвляющийся от межкаскадной связи вход схемы «И».

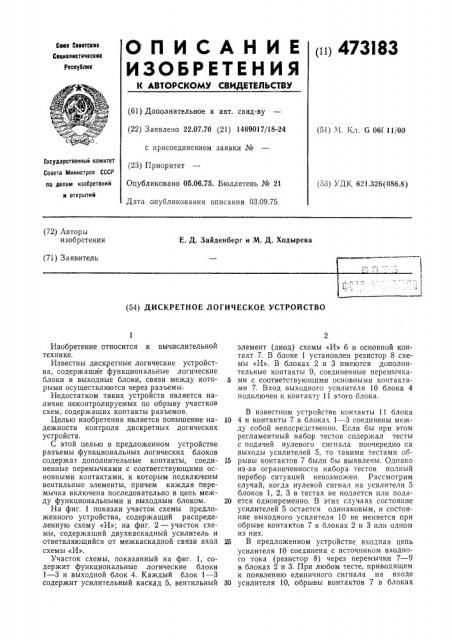

Участок схемы, показанный на фиг. 1, содержит функциональные логические блоки

1 — 3 и выходной блок 4. Каждый блок 1 — 3 содержит усилительный каскад 5, вентильный элемент (диод) схемы «И» 6 и основной контакт 7. В блоке 1 установлен резистор 8 схемы «И». В блоках 2 и 3 имеются дополнительные контакты 9, соединенные перемычка5 ми с соответствующими основными контактами 7. Вход выходного усилителя 10 блока 4 подключен к контакту 11 этого блока.

В известном устройстве контакты 11 блока

10 4 и контакты 7 в блоках 1 — 3 соединены между собой непосредственно. Если бы при этом регламентный набор тестов содержал тесты с подачей нулевого сигнала поочередно па выходы усилителей 5, то такими тестами об15 рывы контактов 7 были бы выявлены. Однако из-за ограниченности набора тестов полный перебор ситуаций невозможен. Рассмотрим случай, когда нулевой сигнал на усилители 5 блоков 1, 2, 3 в тестах не подается или пода20 ется одновременно. В этих случаях состояние усилителей 5 остается одинаковым, и состояние выходного усилителя 10 не меняется при обрыве контактов 7 в блоках 2 и 3 или одном из них.

25 В предложенном устройстве входная цепь усилителя 10 соединена с источником входного тока (резистор 8) через перемычки 7 — 9 в блоках 2 и 3. При любом тесте, приводящем к появлению единичного сигнала на входе

30 усилителя 10, обрывы контактов 7 в блоках

473183

1 — 3, а также дополнительных контактов 9 в блоках 2, 3 выявляются.

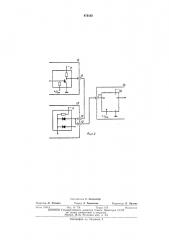

Участок схемы, показанный на фиг. 2, содержит функциональные логические блоки 12, 13 и выходной блок 14. Блок 12 содержит усилитель 15, выход которого подключен к контакту 16. Один из входов схемы «И» 17 блока 13 подключен к контакту 18, соединенному дополнительным контактом 19 перемычкой. Вход выходного усилителя 20 блока 14 подключен к контакту 21.

В известном устройстве контакты 1б, 18 и

21 соединены между собой непосредственно.

Для выявления обрыва контакта 18 необходим тест, при котором единичные сигналы подаются одновременно на вход усилителя 15 и на все остальные схемы «И» 17 (на фиг. 2 показан один дополнительный вход).

В предложенном устройстве входная цепь усилителя 20 соединена с выходом усилителя

15 через перемычку 18, 19. При любом тесте, приводящем к появлению нулевого сигнала на входе усилителя 15, обрыв контактов 18 и

19 выявляется.

Предмет изобретения

Дискретное логическое устройство, содержащее функциональные логические блоки, IO вентильные элементы которых подключены к контактам разъемов, и выходной блок, отл ич а ю щ е е с я тем, что, с целью повышения контролеспособности устройства, разъемы функциональных логических блоков содер15 жат дополнительные контакты, соединенные перемычками с соответствующими основными контактами, подключенными к вентильным элементам; причем перемычка включена последовательно с функциональными и выход20 ным блоками.

473183

Составитель Е. Зайденбсрг

Техред 3. Тараненко

Редактор Л. Утехина

Корректор Л. Орлова

Типография, пр. Сапунова, 2

Заказ 2184 3 Изд. _#_o 778 Тираж 679 Подиис гое

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4 5