Устройство фазирования по циклам

Иллюстрации

Показать всеРеферат

т

О П И С -НИ"Е" ггп 4733!7

Союз Советских

Социалистических

ИЗОБРЕТЕН ИЯ

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 07.08.72 (21) 1816203/26-9 (51) М. Кл. Н 04l 7/08 с присоединением заявки Л

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (23) Приоритет

Опубликовано 05.06.75. Бюллетень № 21

Дата опубликования описания 02.09.75 (53) УДК 621.394.662.2 (088.8) (72) Авторы изобретения

А. Ю. Гордонов и Ю. А. Суровцев (71) Заявитель (54) УСТРОЙСТВО ФАЗ И РОВАН ИЯ ПО ЦИКЛАМ

Изобретение относится к радиотехнике и радиосвязи.

Известно устройство фазирования по циклам, содержащее последовательно соединенные регенератор, числовой регистр, счетчик ошибок и блок управления, которое позволяет выполнять только фазирование по циклам, а для выполнения других логических задач требуются новые устройства.

Цель изобретения — расширение функциональных возможностей устройства — достигается тем, что в предлагаемом устройстве между дополнительным выходом числового регистра и выходом блока управления включены последовательно соединенные дешифратор команд и регистр адреса, выход которого подключен через накопитель ко входу регистра числа, выходы которого, в свою очередь, подключены к соответствующим дополнительным входам числового регистра непосредственно и через блок оперативной памяти, состоящий из последовательно соединенных регистра адреса и накопителя.

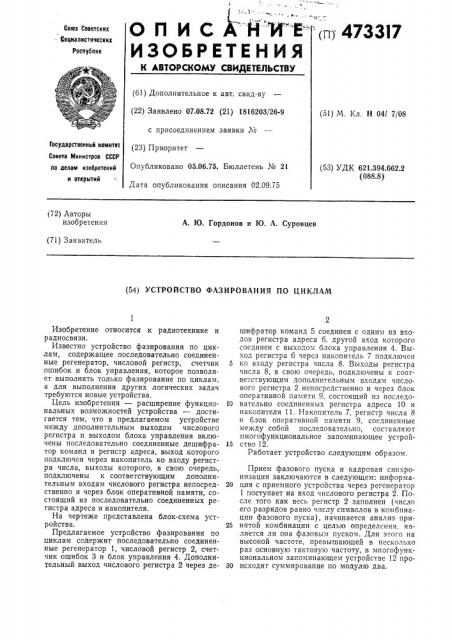

На чертеже представлена блок-схема устройства.

Предлагаемое устройство фазирования по циклам содержит последовательно соединенные регенератор 1, числовой регистр 2, счетчик ошибок 3 и блок управления 4. Дополнительный выход числового регистра 2 через дешифратор команд 5 соединен с одним из входов регистра адреса 6, другой вход которого соединен с выходом блока управления 4. Выход регистра 6 через накопитель 7 подключен

5 ко входу регистра числа 8. Выходы регистра числа 8, в свою очередь, подключены к соответствующим дополнительным входам числового регистра 2 непосредственно и через блок оперативной памяти 9, состоящий из последо10 вательно соединенных регистра адреса 10 и накопителя 11. Накопитель 7, регистр числа 8 и блок оперативной памяти 9, соединенные между собой последовательно, составляют многофункциональное запоминающее устрой15 ство 12, Работает устройство следующим образом.

Прием фазового пуска и кадровая синхронизация заключаются в следующем: информа20 ция с приемного устройства через регенератор

1 поступает на вход числового регистра 2. После того как весь регистр 2 заполнен (число его разрядов равно числу символов в комбинации фазового пуска), начинается анализ при25 нятой комбинации с целью определения, является ли она фазовым пуском. Для этого на высокой частоте, превышающей в несколько раз основную тактовую частоту, в многофункциональном запоминающем устройстве 12 проЗО исходит суммирование по модулю два.

473317!

3-й

М в, ч

11икл такта

1-й

2-й

Команда операции адрес адрес адрес, Запись информации а в накопитель ОЗУ из числового регистра

1 Запись а а

С гитывание эталонного фазового пуска b нз накопителя ОЗУ в числовой регистр

Конъюнкция

Считывание

Запись

Считывание

Считывание эталонного фазового пуска из накопителя ОЗУ в числовой регистр

Лизъюнкция а-1-b

Запись

Считывание

Считывание из первого адреса накопителя ОЗУ обратным кодогя информации аб

Конъюнкция аб (а —,b) Запись

Считывание

Считывание в числовой регистр информации из 2-го адреса накопителя ОЗУ (результата суммирования по модулю два) тьего адреса накопителя 11 считывается в чис; 0â0é регистр 2, где информация сдвигается на один основной такт. После этого цикл повторяется.

Устройство фазирования по циклам, содержащее последовательно соединенные регене10 ратор, числовой регистр, счетчик ошибок и блок управления, отличающееся тем, что, с целью расширения функциональных возможностей, между дополнительным выходом числового регистра и выходом блока управ15 ления включены последовательно соединенные дешифратор команд и регистр адреса, выход которого подключен через накопитель ко входу регистра числа, выходы которого, в свою очередь, подключены к соответствующим

20 дополнительным входам числового регистра непосредственно и через блок оперативной памяти, состоящий из последовательно соединенных регистра адреса и накопителя, Работа по такой микропрограмме происходит благодаря тому, что в накопитель 7 записана соответствующая программа. С него через регистр числа 8 подается команда в регистр адреса 10, и из накопителя 11 выбирается нужное число, с которым выполняется нужная опсрация. В следующий высокочастотный такт с накопителя 7 через регистр числа

8, числовой регистр 2, дешифратор команд 5 подается новая команда в регистр адреса 6 для проведения слсдующеи операции.

С числового регистра 2 результат сложения по модулю два поступает на счетчик ошибок

3. Если этот результат меньше определенного числа, счетчик посылает сигнал на блок управления 4, который выдает команду в регистр адреса 6 на переход на другую микропрограмму (для чего с регистра 6 выбирается соответствующий адрес) .

Если результат сложения IIo модулю два больше определенного числа, с блока управления 4 подается новая команда в такте основной (низкой) частоты, информация с треПредмет изобретения

473317! ! !! ! !

Составитель С. Лукинская

Корректор 3. Тарасова

Техред А. Камышникова

Редактор Б. Федотов

Типография, пр. Сапунова, 2

Заказ 2128 8 Изд. ¹ 784 Тираж 740 Подписное

1ЛНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открыгий

Москва, Ж-35, Раушская наб., д. 4, 5