Устройство для контроля арифметических операций по модулю три

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

474009

Союз Советски

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 02.03.70 (21) 1408419 18-24 (51) М.Кл. G 06f 11 10 с присоединением заявки М

Государственный комитет

Совета Министров СССР оо делам изобретений и открытии (32) 11риоритст—

Опубликовано 14.06.75 Бюллетень М 22

Дата опубликования описания 09.01.76 (53) УДК 681.325. .5 (088.8) (72) А в сор изобрс с!!н5!

Л. И. Шапиро (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АРИФМЕТИЧЕСКИХ

ОПЕРАЦИЙ ПО МОДУЛЮ ТРИ

Известны устройства для контроля арифметических операций по модулю три, содержащсе регистры контрольных кодов операндов, схему свертки, схему умножения контрольных кодов, cxåìó сложения контрольных кодов, схему управления контролем и схему сравнения, в которых контроль операции деления осуществляется путем сравнения контрольного кода делимого с суммой по модулю три контрольного кода остатка от деления и произведения контрольных кодов делителя и частного.

Недостатком известных устройств является гл!экая эффективность контроля операции деления. Сбои или отказы в схемах арифметического устройства, осуществляющих формирование кода частного, в случае равенства контрольного кода делителя модулю три не обняружива!отся, так как в этом случае произведение контрольного кода частного и делителя независимо от наличия ошибок в частном равно модул!о три.

Целью изобретения является повышение эффективности контроля операции деления.

Поставленная цель достигается путем введения в состав устройства трех схем совпадеl!ия и инвертора, соединенных соответствующим образом с другими функциональными узлами устройства.

В устройстве контроль операции деления при неравенстве контрольного кода делителя модулю три осуществляется аналогично контролю в извсстных устройстваx. В случае равенства контрольного кода делителя модулю три в ходе вьшолнс!шя операции производится сложение llo модулю трп сигналов переноса из старшего разряда сумматора арифметического устройства, поступающих в устройство для контроля, с учетом инверсий весов разря10 дов частного, которым эти сигналы переноса соответствуют Ilo сигналу окончания операции деления в устройстве выполняется контроль результатов операции в соответствии со следующим контрольным выражением:

R,.= (R + R ; R,,) шод3, где R,. — - контрольный код делимого;

R — контрольный код частного;

20 R — контрольный код, образованный сложением сип!алов перенося с учетом весовой функции;

-- контрольный код остатка от дслсния.

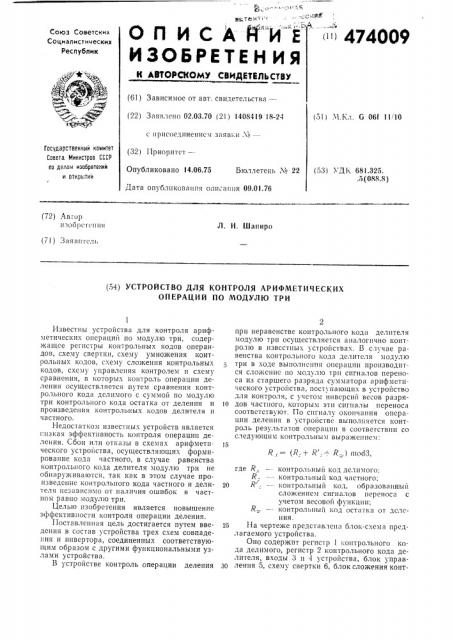

25 На чертеже представлена блок-схема предлагаемого устройства.

Оно содержит регистр 1 контрольного кода делимого, регистр 2 контрольного кода делителя, входы 3 и 4 устройства, блок управз0 ления 5, схему свертки 6, блок сложения конт474009 рольных кодов 7, с»ему сравнен!ни 8, в: од 9 устройства, блок умножения контрольных кодов 10, выход 11 устройства, схемы 12-- 14 совпадения, входы 15 и 1Г>»>còðîéñòBH и инвертор 17.

Контролы1ыс коды операндов, 1!яд которыми производится арифметическая операция, записываются в регистры 1 и 2. При контроле операции деления контрольный код делимого проходит через вход 3 устройства на вход регистра 1, а контрольный код делителя через вход 4 устройства — на вход регистра 2. Если контрольпьш код делителя нс рывеп моду. 1 10 ТРИ, то 0 70I(УПРЯВЛСННЯ 0 IIOC,1C ОКОНЧ сlпия операции деления выдаст ряд сигня10В управления на схему свертки 6, блок сложсIlkI5I I»0HTpoëül1ûx кОдОВ / 11 схсму сраВ!1сния 8. В соответствии с этпмп сигналами первоначально схема свертки 6 определяет код остатка от кода 1!1стцого, поступающего Ilcl CC вход с входа 9 устройства, передает эгог

I(oä остатка Bcl Bход олÎкы ум!!Îжсlllt>l к»III рольпых кодов 10.

Блок умножсши контрольных кодов 10 образует код произведения контрольного кода частного и делителя и псрсдаст его в предварительно установленный в исходное состояние блок сложения контрольных кодов 7, Затем схема свертки 6 по сигналу из блока управления 5 определяет контрольный код от кода остатка, образующегося в арифметическом устройстве в результате выполнения операции деления. Этот контрольный код с выхода схемы свертки 6 поступает в блок сложения контрольных кодов 7. Образовавшаяся сумма контрольных кодов сравнивается схемой сравнения 8 с контрольным кодом делимого, поступающим с выхода регистры 1. В случае неравенства схемы сравнсния выдает на выход 11 сигнал «сбо»>, Если коптролы1ый код делителя равен модулю три, то схемы совпадения 12 формирует сигнал па входе блока управления 5, которьш выдает на первые входы схем 13 и 14 сигнал разрешения переписи в блок сложения контрольныx кодов 7 сигня ,1ов переноса, поступающих пы вторые входы схем 13 и 14 со входа 15 устройства в течение всей операции. Тактовые сигналы сдвигов частного, поступающие на вход 16 устройства, про:»одит через инвертор 17 на третий вход схемы 13 и непосредственно на третий вход схемы 14, В результате этого при тактовых сигналах, соответствующих формированию в арифметическом устройстве значения нечетно-! о разряда частного, открывается схема 13, а при тактовом сигнале, соответству1ощем формированию четного разряда частного, — схема 14.

Таким образом, в ходе выполнения отдельных тактов операции деления поочередно открываются схемы 13 и 14, и сигналы переноса проходят либо через схему 13 на вход старшего разряда блока сложения контрольных кодов 7, либо через схему 14 «а вход младшего разряда этого блока. После окончания

О. 1 I 011 1 и „нц! = O 011100 Ф0.000000101!

0.1100!I

7 654321 — рызря;1ы

>5 yl ill

Z =- 0.011100 (частное) R = 0,12

W = 0.0000001011 (остаток1 R .„ . = =10

Прп осуществлении ко!Проля операции деления приведенных выше чисел возникает си50 туация, когда контрольный код делителя Pv равен модулю контроля три.

В ходе выполнения операции деления сигнал переноса из старшего разряда сумматоры арифметического устройства (АУ) в соотвстЗ5 ствип с известными алгоритмами выполнения ,I ctlllIOII ОПСРсlЦИИ Д01ЖI>Ы Н05! В. I >IT!>C51 Н Ы BXO дс 15 у стройствы при Ollpezeленни значений третьего, четвертого и пятого разрядов частного.

40 В РСЗХ. I Ь! а 1С Э ГОГО IIP Ii I;l I I ОВЬ!Х СПГIIH 7ñlX, co0Iвс!ствующих формированию в АУ значений нсчеп!ых разрядов частного (барс !ьего и пятого), открывается схема 13, и IIH вход

0 Л 0 К а C/1 0Æ C! I È 51 К 011 1 P 0,1 Ь1! Ы X КОДО В / ДВ с1?КД Ы

45 подается код 10>ь ы при тактовом сигнале, соотвествующем формированию в АУ значения четного разряды чяспгого (вгорого), открывается схема 14, и IIH вход блока сло>кения ко!прольных кодов 7 подается код 01>.

50 Таким образом, после окончания операции деления в блоке сложения контрольных кодов 7 формируется код (10 +

+ 01 + 10) mod, 3 = 102, т. е. />х = 10>.

При правильном выполнении операции деле55 ния выполняется контрольное соотношение

R, = (R,+ R + R„,) mod 3, так как 10 (0,1 -,- 10 + 10) mod 3.

Предмет изобретения

Устройство для контроля арифметических операций по модулю три, содержащее регистры контрольного кода делителя и контроль05 ного кода делимого, входы которых соединены

4 операции деления блок управления 5 закрывает схемы 13 и 14 и выдает ряд сигналов управления. По этим сигналам первоначально (хема свертки 6 образует контрольный кодот коды чысп1ог0, поступающего пз арифмети tcского устройства, и осуществляется передач;1 кода с выхода с емы свертки 6 в блок сложения контрольных кодов 7. Затем с:»емы свертки формирует контрольный код от кода

10 остатка, образовавшегося в результате операции деления. Это" контрольньш код также передается в блок сложения контрольных кодов 7, Образовавшаяся сумма контрольных кодов сравнивается схемой сравнения 8 с контрольным кодом делимого, поступающим с выхода рсгистра 1 контрольного кода.

Пример: Х = 0.010111 (делимое), R„=

10 (двоичная систе»!я); У = 0.110011 (дел итсл ь), R Ä =- 11г, 20

474000

Составитель А. Жереиов

Текред М. Семенов

Корректор А. Дзесова

Редактор E. Семанова

Заказ 5998 Изд. <¹ 1511 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, iK-35, Раушскан наб., д. 4/5

МОТ. Загорский филиал соответственно с первым и вторым входами устройства, третий вход которого подключен к первому входу схемы свертки, первый выход которой соединен с первым входом блока сложения контрольных кодов, второй вход которого подключен к выходу блока умножения контрольных кодов, первый и второй входы которого соединены соответственно с первым выходом контрольного делителя и со вторым выходом схемы свертки, выходы регистра контрольного кода делимого и блока сложения контрольных кодов соединены соответственно с первым и вторым входами схемы сравнения, выход которой подключен к выходу устройства, третий вход схемы сравнения соединен с первым выходом блока управления, второй н третий выходы которого подключены соответственно ко второму входу схемы свсртки н к

Г

1

1

1 ! ! ! !

I !

1

1

1

1

1 третьему входу блока сложения контрольных кодов, от гичающееся тем, что, с целью повышения эффективности контроля операции деления, в него введены схемы совпадения н нн5 вертор, причем второй выход регистра контрольного кода делителя через первую схему совпадения соединен со входом блока управления, четвертьш выход которого подключен к первым входам второй и третьей схем сов10 падения, вторые входы которых соединены с четвертым входом устройства, пятый вход которого подключен ко входу ннвертора и и третьему входу третьей схемы совпадення, выход инвертора подключен к третьему входу

15 второй схемы совпадения, выход которой соединен со входом старшего разряда блока c;Ioжения, вход младшего разряда которого подключен к выходу третьей схемы совпадения.