Устройство для асинхронного ввода двоичной информации со стаффингом в цифровой канал

Иллюстрации

Показать всеРеферат

Союз Советсиии

СОЦИаЛИСтИНЕСКИ>1

Республик

ОП ИСА

ИЗОЫ ЕтИН ИЯ, К АВТОРСКОМУ СВИДИЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.01.74 (21) 1987298/26-9 (51) М. Кл. Н 04j 1/14 с присоединением заявки №вЂ”

Государственный комитет

Совета Йинистроа СССР оо делам изобретений и откр о!т !! и (23) Приоритет—

Опубликовано 14.06.75. (53) УДК 621.376,56 (088.8) Б!Оллетен1,,х, е 22

Дата опубликоваш я описания 07.01.76 (72) Автор изобретен и я

В. Г. Левин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО ВВОДА

ДВОИЧНОЙ ИНФОРМАЦИИ СО СТАФФИНГОМ

В ЦИФРОВОЙ КАНАЛ

Изобретение относится к электросвязи и может быть использовано в аппаратуре асинхронной передачи двоичной информации.

Известно устройство для асинхронного ввода двоичной информации со стаффингом в цифровой канал, содержащее блок памяти, последовательно соединенный с фазовым компаратором, к которому подключен блок формирования команд.

Однако известное устройство обладает значительными низкочастотными фазовыми флуктуациями, попадающими в полосу пропускания системы фазовой автоподстройки частоты на прием лом конце.

С целью уменьшения низкочастотных фазовых флуктуаций выходного сигнала в предлагаемом устройстве второй выход блока па мяти через дополнительно введенный фазовый модулятор с источником модулирующего синусоидальпого напри>копия подключен к соответствующему входу фазового компаратора.

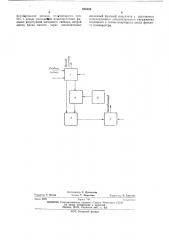

Г1а чертеже представлена блок-схема предлагаемого устройства для асинхронного !ввода двоичной информации со стаффингом в цифровой канал.

Предлагаемое устройство содержит последовательно соединенные блок 1 памяти, фазовый компаратор 2 и блок 3 формирования команд. Бто:o!1 выход блока 1 памяти через ф !!30вьl!! з10д л !! Ор 4, У1!равд !!ем!>1 !! 11OT0 11! IIком 5 спнусоидального модулирующего напряжения 5, соединен с другим входом фазового коипаратора 2.

Сигналы из блока памяти, разность фаз между которыкlп хяр актер п31 ет запас !!11!1!Ормации, хранящейся в нем, поступают на один из входов фазового компаратора 2, а на дру гой вход — через управляемый источник 5 го модулирующего синусоидального напряжения фазовый модулятор 4, представляющий собой устройство управляемой задержки фронта импульса, поступающего из блока памяти на фазовый компаратор 2, с выхода которого сигналы поступают в блок 3 формированн!! команд.

Путем соответствующего Bl loop 1 модулирующей частоты низкочастотные фазовыс рлуктуации преооразуются в флуктуации бо„ и лее высоких частот, не попадающие в полосу пропускан1гя системы фазовой азтоподстройки частоты, в результате чего фазовые флуктуации существенно сей!Яоляются. 5 Предмет изобретения

Устройство для ас!енхроп;!Ого ввода двоич

: ой информации со OTaIpg«III в цифровой

I;a!12.1, содержащее последовательно соединеп, о le 0:IoI< IIQ,. !I!IT!I, фазовый компаратор II блок

474110

D odeou (:иана

Составитель С. Лукинскаи

Техред Т. Миронова

Редактор Т. Янова

Коррекгор Е. Хмелева

Заказ 5999 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

МОТ, Загорский филиал

3 формирования команд, отлцчаюи ееся тем, что, с целью у.мепьщеФия низкочастотных фазовых флуктуаций выходного сипнала, второй выход блока памяти через дополнительно

4 введенный фазовый модулятор с источником модулирующего сипусоидального напряжения подключен к соответствующему входу фазового компа ратора.