Цифровой частотомер с автоматическим выбором пределов измерения

Иллюстрации

Показать всеРеферат

< 147476

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 30.01.73 (21) 1875895/18-10 (51) М. Кл. 6 01 r 23 10 с присоединением заявки №вЂ”

Государственный комитет

Совета Министров СССР (32) Приоритет—

Опубликовано 25.06.75. Бюллетень № 23

Дата опубликования описания 10.02.76 (53) УДК 621.317.761 (088.8) по делам изобретений и открытий (72) Авторы изобретения

H. В. Кирианаки и С. С. Кочеркевич (71) Заявитель (54) ЦИФРОВОИ ЧАСТОТОМЕР

С АВТОМАТИЧЕСКИМ ВЫБОРОМ

ПРЕДЕЛОВ ИЗМЕРЕНИЯ

Изобретение относится к электрос1змез!1тельной технике и может быть иепользовано для !повышения точности и быстродсйств:1я ци!фравых частотомерав.

Из!ве стный цифровой частотомер с автоматическим выбором пределав измерет!ия, содержащий входной формираватель ихгпульсов, подключенный к десятичнаму .счетчггку импульсов через временной селектор, управляющий !вхо!д которого соединен с выходом форм!ирующето триггера, триггер запуска, устройство вьввода информации, связанное с !выходами счетчика и триггера запоминания «1» старшего разряда счетчика, и генератор ооразцового интервала времени, подключенный к вход у формирователя ряда возрастающих во времени образцовых интервалов времени.

Предлагаемый частотомер отличается от из!вестных тем, что он снабжен упра!вляющим триггером, дешифратором состояния «1» последнего и «9» предпоследнего разрядов счетчика и блоком формироваттия ряда ооразцоBbIx интер!валов времени (гдервый член равен минимальному времени измерения, второй— в девять раз больше первого, а каждый из последующих ра!вен предыдущему, узетиченному в десять раз), образаванного сдвигавым репистром, линейкой декадных делителей частоты следования llмпульсав, двумя схемами

«ИЛИ», exch:o! I «И» II c c.»o!! и з1;l л!.сиз-:Ioтенцнальных к Ilo !сй, Входь! котоpых подклlочены к выходам рсгистра 11 делителе!! частоты, а зыходы — к входам первой схемы

5 «ИЛИ», выходом соединенной с первым входом .второй схемы «ИЛИ» 11 первым чходом схемы «И». выход которой овязан с запрещающим .входом форм:1ру1ощего триггера, а второй вход — с !вторым входох1 второй схемы

10 «ИЛИ»,п выходо1м упра вля1ощеro триггера, первый вход которого подключен к выходу формирующего триггера, а второй — к выходу дешпфратора, причем, выход триггера запуска соединен с разрешающим входом формирующего триггера, входом сброса,в «1» первого делителя частоты и вхадами сброса в «О» остальных делителей частоты, а выход второй схемы

«ИЛИ» подкл1очеH к входу регистра.

20 Такое выполнен 1с устройства зоз!валяет повысить его точность и быстродействие.

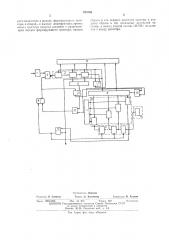

На чертеже приведена блок-схема:1рсдлагаемого устройства.

Устройство состоит нз входного формпрователя их!пульсов 1, временного селектора 2, десятичного счет -1пка импульсав 8, формирующего триггера 4, управляющего триггера 5, дешифратора б состояния «1» !последнего и

«9» предпоследнего разрядов счетчика 3, триг30 гера 7 запоминания «1» старшего разряда

474760 счетчика 8, блока формирования ряда возрастающих во времени образцовых интервалов времени

Т, + 97; + 907; .+ . 9 . 10 Т о. разованного сдиговым регистром 8, линейкой 9 декадных делителей частоты следования импульсов, схемой 10 импульсно-потенциальных ключей, первой схемой «ИЛИ» И, схемой

«И» 12 и второй схемой «ИЛИ» 18, триггера запу"ка 14, генератора 15 наименьшего образцо вого интер вала времени TI, и устройства вызода информации 16.

Устройспво работает следующим образом.

По сигналу «Пуск» триггер за пуска 14 принимает исходное со стояние, а в счетчике 8, триггере 7 и регистре 8 прая сходит сброс в

«О». Первый после «Пуска» им пульс т1з генератора 15, поступающий на второй вход триггера 14, перебрасы вает триггер 14. Выходной импульс триггера 14 за пускает формирующий

lpHl.I.cp 4 и произ водит сорос-установку, делителей линейки 9, причем в первый делитель занавесится «1», а остальные — «0». Выходным пмпуль сом триггера 4 открывается селектор 2, я на счетчик 8, формирователь 1 поступают импульсы входной частоты. Этим же импульсом триггер 5 устанавливается,в такое состояние, IlpH котором его выход за кры вает схему совпадения 12 и заносит «1» посредством схемы «ИЛИ» 18,в первый разряд регистра 8.

Вследствие этого импульсно- потенциальный ключ схемы 10, соединенный с этим разрядом, оказывается открытым и второй после «Пуска» им пульс генератора 15 проходит через этот ключ на выход схемы «ИЛИ» 11. Так образуется первый образцовый HHTcpIBBJI времени (первый предел) Ti,. Ежели схема «И» 12 закрыта упра вляющим триггером 5, выходной импулыс схемы «ИЛИ» ll не проходит на ее выход и не перебрасьнвает трипгер 4. Счет импульсов входной ча "таты illpozoлжается уже на втором пределе. Выходной импульс схемы 11 посредством схемы «ИЛИ» производит в регистре 8 перенос «1» в следующий разряд, открывая следующий импульсно-потенциальный ключ схемы 10.

После .прихода на;пер вый делитель линейки 9 девяти импульса в Ic периодом Т на его выходе

IIIîÿlBëÿåTcÿ импульс второго предела, который че|рез .открытый второй импульсно- потенц иалbный ключ схемы 10 .проходит на выход схемы

1l. Второй предел ра вен 10 TI,.

Если у пра(вляющий три пгер 5 продолжает удержи вать схему 12 в закрытом состоянии, то счет им пуль сов в одной частоты продолжаегся, а импульс |второго предела через схему

18 производит в реги стре 8,перенос «1» в треTlHII разряд, откры вая третий иипульсно- потенциальный ключ схемы 10. Ес,ти сразу же после окончания импульса второго предела происходит за полнение,декад счетчика 8 до .состояния 19000 ..., то срабатывает дешифратор б и перебрасывает управляющий триггер 5, кото ый открывает схему 12. Так как импульс второго предела прошел до того, KBK QTKpblлась схема 12, то счет продолжается до .-.IpHхода импульса третьего предела, при этом десятичный счетчик 8 переполняется, устанавливает в «1» триггер 7 и продолжает счет, Счет шк 8 вновь заполняется до некоторого состояния, однако его переполнение не происходит, так,как им пульс третьего предела переорасы10 вает триггер 4, селектор 2 закрывается и счет и миул ысо в прекр ащает|ся.

Для значений частот, больших 1 - 10 вРе мя измерения устанав.тивается таким, что «1» старшего разряда всегда находится в тригге15 ре 7, при значениях частот, немного меньших

1 10, Bpeola измерения уста|навливается так:гм же, а вся информация находится в счетчике 8. При этом погрешно сть измерения не меняется.

Процесс измерения частоты,и процесс определения времени измерения происходят одновременно, при этом сигналом определения времени измерения служит не переполнение счетчика, а его промежуточное состояние, вы25 орапное таким образом, что измерение частот, кратных 1 1C", происходит,с максимально возможной для данного частотомера точностью и без потери информации.

30 Предмет изобретения

Цифра|вой частотоьмер с автоматическим выбором сlpcgc;IolB измерения, содержащий входной формирователь импульсов, подключенный к десятичному счетчику импульсов че35 рез временной селектор, управляющий вход которого соединен с выходом формирующего триггера, триггер запуска, устройспво вывода информации, с вязанное с выходами счетчика и триггера запоминания «1» старшего разряда

40 счетчи ка, и генератор образцового интервала зрсмсни, по дключенный к .входу формирователя ряда iB03растающих Во времени образцовых интер валов времени, отличающийся тем, что, с целью по вышения точности и быстро45 действия, он снабжен управляющим триггером, дешифратором состояния «1» последнего и «9» предпоследне го разрядов счетчика и блоком фсрмирования ряда образцовых интервала в времени (первый член равен мини50 мальному времени измерения,,второй — в девять раз больше пер|ваго, а каждый из последующих равен предыдущему, увеличенному в десять,раз), образован ного сдвиговым регистром, линейкой декадных делителей частоты

55 следования импульсов, двумя схемами «ИЛИ», схемой «И» и схемой импульсно-потенциальных ключей, входы которых подключены к выходам регистра и делителей частоты, а выходы — к входам пер вой схемы «ИЛИ», вы60 ходом соединенной с перовым входом второй схемы «ИЛИ» и первым входом схемы «И», выход которой связан с за прещающим входом формирующего триггера, а второй вход — с вторым входом второй схемы «ИЛИ» и выхо55 дом управляющего триггера, первый вход кото474760

Составитель Лившиц

Техред Л. Казачкова

Редактор О. Степина

Корректор В. Гутиан

Заказ 1289/1848 Изд. М 812 Тираж 902 Падлшснос

ЦНИИПИ Государственного комитета Совета Мин«стров СССР по делам изобретений н открыт.ш

Москва, К-35, Раушская наб., д. 4/5

Т«п. Харви. фил, пред. «Латент»

РОГО поде. 11очеп 1; Выходу форъ111p) ющего триГгера, а второй — к выходу дешифратора, прпчез1 выход тр иггера запуска соединен с разреи1ающим входом формирующего триггера, входом сбзо "а в «1» первого дедитеав частоты и вхоДаиип СбРОСа В «0» ОСтаЛЬНЫХ ДСПИтетЕй Частоты, а выход второй схемы «11, П1» иодкаюч с н к входу регистра.