Устройство для вычисления тригонометрических функций

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

- (11) 4748m I

Союз Советских

Социалистических

Республик (61) Дополнительное к авт . свпд-ву— (22) Заявлено 21.1!.72 (21) 1847801/18-24 (51) Ч. Кл. G 061 15/34 с присоединением заявки ¹â€”

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Пр ио р итет—

Опубликовано 25.06.75. Бюллетень ¹ 23

Дата опубликования описания 13.01.76 (53) УД К 68 1.325.66 (088.8) (72) Авторы изобретения

Р. П. Половинкин, А. И. Пономарев, С. М. Старобинец, Н. Е. Фролов и Г. А. Бурлака (71) Заявите.!b (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств автоматики и ЗЦВМ.

Известно устройство для вычисления тригонометрических функций, содержащее два сдвигающих регистра, преобразователи прямого кода в дополнительный, два последовательных комбинационных сумматора, счетчик итераций, дешифратор, схемы выдачи, схему задания констант, двоичный счетчик, схему сравнения, схемы И, ИЛИ, триггеры, cveìó управления, причем выходы двоичного счетчика связаны с )входами схемы сра)внсния, другие входы которой подключены к выходам счетчика итераций, связанных с входами дешифратора, соответствующие выходы которого связаны с входами двух схем выдачи и с входами схемы задания констант, Выходы которого соединены с входами первого сдвигающего регистра, другие входы схемы выдачи связаны с выходами первого и второго сдвигающих регистров, выходы последних разрядов,которых связаны с одним из входов первой и,второй схем И соответственно, выход первой схемы И связан с входом первого преобразователя прямого кода в дополнитель»ый, выход которого связан с одним из входов первого последовательного комбинацио-I»oro сумматора, выход которого подключен к выходу первого сдвигающего регистра, выход второй схемы И связан с входом второго преобразователя прямого кода В дополн:)тельный, выход которого соединен с одним из входов второго последовательного комб»»ацио»ного сумматора, выход которого сзязан с в одом второго сдвигающего регистра.

Недоста гком известного устройства является наличие отдельных регистров для хранения промежуточных величин вычислен»й и необходимость производить перед каждым сложечием сдвиги содержимого разрядов, что усложняет схему устройства.

Для упрощения предлагаемого устройства в нем выход первой схемы выдачи с одним из входов третьей» четвертой схем И, а выход третьей схемы 11 связан с входом первого триггера, выход которого связан с од»им из входов пятой схемы И, выходы четвертой

20 и пятой схем И связаны с входами первой схемы ИЛИ, третий вход которой coca)I»e!I с выходом шестой схемы И, один,пз входов которой связан с выходом последнего разряда первого сдв»гающего регистра, выход первой 5 схемы ИЛИ связан с входом третьего преобразОВателя прял)ОГО кода В дополнительный, ВЫХОД КотоРОГО ПОДК1ЮЧЕ!! K ДРУГОЛ)У ВХОДУ второго последователь»ого комби»ацпо»»ого сумматора, а выход второй схемы выдачи соединен с од»»м»з входов седьз)о)! и .Восьз)ой

47481!

Если Хо=о, Уо=о, Чо=, в= — $1дп о/ 1, то .13 lп-ном п!ягс

Х„, = И, со$ 5 - Л х„;

У: — Ао $1п Ф + 5yÄ,.

Если Хо -— — x, у = ) о, q;o — — О, е/ = SI <>tT) ; то на т-ом шаге; 60

) о

55 схем И, выход седьмой схемы И связан с входом второго триггера, выход которого câÿçàa с одним нз входов девятой схемы И, выходы восьмой и девятой схем II соединены с входами второй схемы ИЛИ, третий вход которой связан с выходом десятой схемы И, один из входов которой связан с выходом последнего разряда второго сдвигающего регистра, а выход второй схемы ИЛИ связан с входом четвертого преобразователя прямого кода в дополнительный, выход которого связан с одним из входов девятой схемы И, выходы восьмой и девятой схем И соединены со входап второй схемы ИЛИ, третий вход которой подключен к выходу девятой схемы И, один из входов которой связан с выходом Iloследнсго разряда второго сдвигающсго регистра, а выход второй схемы ИЛИ соед!шсн со входом четвертого преобразователя прямого кода в дополнительный, выход которого связан с другим входом первого последовательного комбинационного сумматора входы управления с.iâèãàþùaõ регистров, двоичного счетч IIKc7, счетчика итераций, преобразователей прямого кода в дополнительный и другис входы всех схем И подключс:!ы к соответствующим выходам схс» управлcaèÿ.

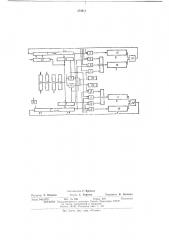

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит сдaíãàioùïå регистры 1 и 2, схемы И 3 — 12, схемы ИЛИ 13 и

14, преобразователи 15 — 18 прямого кода в дополнительный, последовательные комоинационные сумматоры 19 и 20, схемы выдачи 21 и 22, триггеры 23 и 24, двоичный счетчик 25, схему сравне 1ия 26, счетчик:1тераций 27, дешифратор 28, схс»у 29 задяння констант, схс»у управления 30.

Устройство позволяет вычислить одновре40 . IciIH0 тр ГottoitcTpHH!сскнс функц:.1. 1 /Г/> sill ф

cos tI: 1.7н ai.ctp и 1 1.: /

Для вычисления этих тригонометрических зависимостей используют итерацно:1!1ыс фор,,15 мулы; где гп — чи,7o итерации, определяется заданной точностью вычислений и в конкрет.toit устройстве постоянно;

lг — коэффициент, зависящий только от количсcTBa шагов

/г.= 11 j 1 1- 2

Ьх„,Ьу„,Ьл, „Ьу„, — допустимые по грешности вычислений, зависящие от количества шагов и точности вычислений.

Рассмотрим работу устройства при вычисл Itlirl 1. о sill !1;, /c .p cos ф.

В управляющем устройстве работа на первом и на всех остальных шагах реализуется одинакОВО, поэтому рассмотрим работу устройства на 1-ом шаге итераций.

Перед началом вычислений в младших и разрядах регистра 1 записано число Х/, в остальных разрядах — нули. B младших и разрядах регистра 2 записано число ) / 1, в старших и разрядах — 11>/ 1, на счетчике итераций 27 записано число i — 1, а на двоичном счетчике 25 — n, преобразователи кол!>!! 15 — 18 установ 7сны на нсрс.1ачу. прямогo кода, триггеры 23 i! 24 — в «О».

По сигналам нз устройства управления 30 выполняются с.7cäóþùttå операции: прибав7ястся «!» к счстчнкч нтсрац:1й 2:, о!ь. Iастс>1 из схемы 29 задания констант в старшие п

pa3pH;10B pBBilcTpa 1 чнс;1О, p IBlioe arctic ес этого ч 1сла vcTaltoB;Ipll на счстчи(лр ке 27);

Г "ли Ч!/ !)О (анализ! рустся з-iai «2» п-го

01!зр>1ла регистра 2), то уста.1авлнва1от iipeобразоватсль кола 16 на передачу допол:1итс II НОГО КО ta, а ЕСЛИ (fc <О, тО уСтапаВЛНBcl10T IlpBoopaa0BclTc; 17 i!a IIppc Ia ii доно.7ггсльного кода.

Одновременно подаются упрявля1ощие сигнал»1 c7B tlpoB ilcl регистры 1 н 2, прнбавлс IIIH «1» к лвоичному счетчику 25 и разрешающие сигналы на схемы 3, 4, 9 и б, ПОКс! IP НОЯБ !ITCH СИГ!13.! Ня ВЫХОДС СХЕМЫ

cpaBiIPlII1H 26 /сигнал совпадения содержимого счетчиков 2э и 27).

После этого полается управляющий сигнал на схс»ы И 11 и 12, что,лает возмо>кно:ть УcTcliIoBIITB тРиггеР 23 в состои:tèc «О», ес;ш Ус 1 ) О, н состояние «1», если ) / (О, 3 триггер 24 — в состояние «О», если

Х; )О, ll Ocòîaaèc «1», если Х; l (О, так как к этому времени на выходе схемы выдачи 22 уста !овлсн знак числя Х/ 1, а на выходе схемы выдачи 21 — знак числа ) /

Далее олноврсмснно подаются управляющие сигналы сдвигов на рег!истры 1 и 2, сигнал прибавления «1», счетчику 25 и разрешающие CIIr»aлы на схемы 3, 7, 8 и 4, пока не появится сигнал на выходе счетчика 25, и обнуляются преобразователи 15 — 18. Теперь

В CTclplliHÅ /l ряэрядОВ рЕГИСтра 1 ЗаПИСаНО число Х/= Х; + е!) / 2 " ", в младшие и разрялов регистра 1 — ч:!ела ягс1о 2

> >

В ".тарш;!с и разрялав раг:!стра 2 -- числа

У;= У; — е;Х, 12 — 1, в млалшие и раз;-.ялов регистра 2 — число тру

Если раисе было ср; 0, то преобразователь 17 устанавливают на передачу лополнитсльнага кода;

Олновременно подаются сигналы слвигов на регистры 1 и 2, сигналы прибавления «1» к двойному счетчику 25 и разрешающи сигналы на схемы И 10 и 4. Эта операция выполняется до тех пор, пока не появится выхолной сигнал на двоичном счетчике 25. Затем сбрасываются преобразователи 12 — !8, проверяется состояние т-го выхода лешифратора 28: если iiB его выхоле сигнал логической ел1шицы, то конец работы, а есл логического нуля, то, Срсхол к (1+ 1)-ому шагу итераций.

После nz-го шага в и млалших разрялях рсгистра 1 установлено число Х,.„= /гр cos ф—

+ЛХ„„Я в п младших разряЛаx регистра

2 ч:!ело У„, = /гр 31171!1 + Лу„,.

Рассмотрим работу устройства пр:! вычис:le!I:ш функций Bt cfg — и k )/. -

Начальныс состояния всех блоков такие

>кс, как при вычислении функций /ар s!17 4. и

ko соз Ф. Работа устройства аналоги ша работе при вычислении функций игр sit7 ): и

ko cos 1!! за исключс lltci! слелую!цего; на

1-Oil шаге при вычислении Х;, У; анализирует(>! 3, 121" !Ic ((; (t, я У, t > co:Icpæ Iiiol и-ГО разряда регистра 2); если I ; . >О, то IlpeОаразавате Ih I(070B 17 уCTBII 2Bл:!Ва!От;!а реЛЯчу Лополнителы!ага кода, если У; (О. то н реобргlЗОВатсль 16 3>стйи Явл ива!От 111! Iicрелачу лополнителы ого кола, а перел Вычис—

te;t;te>i !с;, если было У; !(О, то пр образоВатель 16 уста11явливают 1 !2 псрелачу лаполIlBòcëüïîãо кола.

Пас:lс ьп-ГО иlяГя В zz itлялших ряЗрялах р t истра 1 уcTBtioB7cito числоХ,.„=/г1> л- - —; — у - —

/ — ЛХ.„, а В и старших разрялах реги т1а 2

11

1 . т11! 10В.7 .Io >!1! c 10 11:»> = ЯГС1С > + Л< >>, Пре ti1ет изобретения

Устройство лля вычисления тригонометр:1ческих функций. Солер>кащее лва слвигающпх регистра, преобразователи прямого кода В дополнительный, лва последовательных комОинациош!ых сумматора, счетчик итераций, лешифратар, схемы .выдачи, схему залания констант, двоичный счстч:!к, схему cрявнс,t,".ÿ, схемы И, ИЛИ тр;!ггеры, схему управлс5 !

О

Зо

60 нl, я, причем r3h xo7û ЛГ>а:t÷!10. 0, ч тч"..кя 33113 2!! Ь(ВХОДЯ >> : С Х С . >! Ь! С P 2 В:. I C 1: 1 Я, Л Р У Г 11 Е В Х 0лы которой полкл1очсны,к выходам счетчика итераций, сзяз211!ihix. с вхолами лешпфратора, соотвстствуюн.ис выхолы которого связаны с вхолами лвуx схем выдачи и с вхоламп схемы задания констант> выходы которой соединены с вхолами первого слвигающего pe-! I1CTP2, ЛР ГИС ВХОДЫ С. С \! ВЫЛЯЧИ СВЯЗЯНЫ С выхолами первого и Второго слвигающпх регистров, выходы послеЛних разрялов которых связаны с оЛ!им из вхоЛов первой 11 второй схем И соответственно, Выхол первой схемы

И связан с вхолом первого прсобразователя п17Я маго I .032 B лot107! t;I TP 7bil hill. В>Ь1хал IfoTQрого связа;! с одним из вхолов первого Iloследоватсльног0 комбинационного сумматора, выхол которого полключен к вхолу первого слвпгающсго рег11 стра, выход второй схемы

И связа (с Bxo;ioil второго преобразов11тсля прямого кола в лопо7íèòñëüíûé, выход которого соединен с одним из вколов второго послеловательного комбинационного сумматора, выхол которого связан с вхаЛом второго слвигающего регистра, ат.111чаю11;ессл тем, что, с целью упроще11:,!я устройства. В нем выхол первой схемы выдачи связан с олним из Вхолов третьей и четвертой схем 11, я Выкал третьей схемы И саед!шеи с входом первого триггера, выхол которого связан с одним из входов пятой схемы 11, выхолы четвертой и пятоЙ схс. I II связя:!ы с вхо:!ам:! первой схемы ИЛИ, трет1й вхол которой сосл1псн г. выхолом шестой схемы И, адин из входов которой связан с выходом послслнсго разряла перзога cËB,tão!otiipго регистра, Выход первой схемы ИЛ11 сзяз21! с " ;олам третьего рсобРBÇOB 1ТС fll IIPЯT!OPО I OЛ;1 B ioiio;1:1!!TC7bllblй, выкал ко-,араго полксиа:!сн к лругому вхолу

BTopoI o пас7сл;!BBTсльнага i а:>1б:.t:!;1!1!to>1;!Oco сх 1 >!BTОРЯ, и выкал вто1701! сxcil ht ВВ1лач!t

=Вяз 1:I с Вхо 711 71:I сель.>!Ой 11 Восьмой cxc. l I, Выхол се,ьмой схемы 11 саелинен с Вхалом второго триггера, выхол которого связа1! с

Олi!им:13 ВX070В лCВtlТОй C СмЫ 11, ВЬIХОл1>!

Bocbxioli и Лсвятой схем 11 соединены с Входами второй схемы 11,1И, третий вход которой палключс:! к выкал десятой схемы II, à Ill!1

ИЗ ВХОЛОВ КОТОРО!I СВЯ311!i С 131>!ХОЛО >. !110СГ1С:1него разряля второго слв;1гающсга pcl ltcTp2, р выхол второй схемы 11Л11 сасл:11ii:l с Вхалом четвертога преобразователя прямого кала в лополнптельный, выхол которого связа1!

С ЛР >>ГИМ В:>;ОЛОМ ПЕРВОГО llOC, 1 СЛОВ ЯТС;! Ьнаго комбинационного сумматора, входы управлс;!ия слв:.1ганащ1tx рег. !стров, лг>оичного счетчика, счетчика итерац ш. преобразователей прямого кола в лопал!и!телы!ый и лруг;!е вхолы всех схем II палключе:!ы к саотВетствующ11м Выхолям схем управлс:шя.

474811

Составитель Г. Бурлака

Редактор Т. Иванова Тскред T. Курилко Корректор И. Сив1кина

Заказ 940/l379 Изд. М 838 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретешш и открытий

Москва,,К-35, Раушская наб., д. 1 5

Тип. :арьк. фил. пред. «Патент»