Запоминающее устройство

Иллюстрации

Показать всеРеферат

3Океeqw %л

О П И С."АИ"--И- Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социал истичесних

Реслублин (и) 474845

К АВТОРСКОМУ СВИДИТИЛЬСУВУ (61) Дополнительное к авт. свяд-ву (22) Заявлеио16.06.72 (21)1797268/18-24

< с присоединением заявки № (51) М. Кл.

611 g 11/00

Государственный комитет

Совета Мннистрии СССР ии делам изобретений н открытий (23) Приоритет (43) Опубликовано 25.06.75.Бюллетень № 23 (45} Дата опубликования описания03 06.76 (53) УДК 681.327.025 (088. 8 ) (72) Автор изобретения

Г. Г. Мамджян (73) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к блокам памяти цифровых вычислительных машин и системам обработки информации, работоспособность которых должна сохраняться в широком диапазоне изменения внешних условий (температуры, напряжений питания).

Известны запоминающие устройства (3У), содержащие накопитель, блок синхронизации, выход которого соединен с адресным блоком управления, и блок записи-воспроизведения, 1О ,соединенный с накопителем и блоком синхро-. низации, в которых для повышения отношения сигнал/помеха на входе усилителя,считывания (УС) в диапазоне температур управление накопителем производится токами, выборки, та изменяюшимися по определенному закону в зависимости от температуры окружаюшей средыа

В известных устройствах производится косвенное отслеживание токами выборки в дна- g0 аазоне температур за отношением сигнал/ттомеха на выхсде матриц памяти накопителя.

Точное воспроизведение требуемых законов изменения токов выборки or температуры затруднено из-за сложного и многофакторно- хо го влияния температуры на процессы в маг;нитных элементах памяти, а линеаризация этих законов ведет к потере точности.

Цель изобретения - повышение информа-! ционной надежности 3У. Достигается это тем, что в устройство введены дополнитель ный блок синхронизации, состоящий из генератора тактов и контрольных обращений, счетчика контрольных обращений и блока режи ма, блок адаптации, содержащий усилитель воспроизведения, преобразователь амплитуда! код, регистр делителя, блок деления, буфер ный регистр, блок сравнения, ; эле мент ИЛИ, два элемента И, реверсивныйсчетчик, де преобразователя код-напряжение, сумматор.

Блок адаптации обеспечивает дискретное оптимальное управление токами выборки, а

; дополнительный блок синхронизации производит выбор режима контроль" или работа" и управляет работой блока адаптации. B адрес ный блок управления введены два дополнителт ных адресных канала, причем в первом дополнительном адресном канале IIocToRBHo записан "0, а во втором — 1 . В дополнительном рВЭрйде накопителя постоянно записан тяжелый код (например, шахматный по-рядок - по всем четным адресам - "1", по нечетным адресам - "0 ).

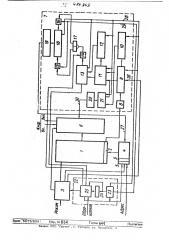

Ка чертеже изображена блок-»схема 3У.

3апоминакицее устройство содержит накокитель 1 с дополнительным разрядом 2, блок синхронизации 3, адресный блок управлении 4 с двумя дополнительными адрес.ными каналами 5, блок записи-воспроиэведе- 1О иия информации 6, блок адаптации 7, состояший из усилителя воспроизведения 8, преобразователя амплитуда-код;9, регистра дели-,: теля 10, блока деления 11, буферного реги ( стра 12, блока сравнения 13, элемента. ИДИ, Р

14, элементов ГИ 15,16, триггера 17, ре-» версивного счетчика 18, преобразователей код-напряжение 19 и 20 и сумматора 21.

Кроме того, в 3У введен дополнительный блок синхронизации 22, состояший из генератора 23 тактов и контрольных обращений, счетчика 24 контрольных обращений и блока режима 25.

3У работает, следующим образом. Перед, началом работы . устайаыивается исходное

23 состояние устройства ф.гому состояние соответствует установка блока режима 25 в режим контроль, обнуление всех триггеров схемы ЗУ и установка реверсивного счетчи30 .ка 18 в состояние, соответствующее коду

2, где пЪ вЂ” чйсло разрядов регистра делителя. 10, буферного регистра 12 и ревер- сивного счетчика 18. При этом преобразователь код-напряжение.19 выдает усредненное значение управляющего напряжения и соответственно исходное значение токов выборки равно — м""+ м . Затем начин нается первый цикл адаптации, состоящий из двух контрольных обращений по дополни- 4О тельным адресным каналам., Считанные при контрольных обращениях сигналы поступают, на линейный усилитель воспроизведения 8 блока адаптации 7, с. выхода которого усиленный сигнал подается на преобразователь,ц амплитуда-код 9, Работой преобразователя амплитуда-код 9 управляет строб с выхода усилителей воспроизведения основного блока синхронизации 3 (провод 26),. разрешающий работу преобразователя 9 только во ® время действия полезного считанного сигнала. При первом контрольном обращении амп-, литуда считанной помехи (сигнал "0") Я, 1 преобразуется в цифровую форму преобразова-, телей амплитуда-код 9 и переписывается 55

- ре1 истр делителя 10. При втором контI рольном обращении первого цикла амплитуда считанного сигнала 1"Р > преобрзуежF ся в цифровую форму преобразователем амп- литуда-код 9 и,в блоке деления 11 вычис- 60 )4 ляется отношение сигнал/помеха, Д"

Я Jüj.

О

Выходы блока деления 11 и буфепного регистра 12 соединены с входами блока сравнения 13. Так как ripe первом цикле адаптации буферный регистр 12 был обнулен„п1> () O и блок сравнения всегда определяет, что

P" р Д . На выходе блока сравне ),1-1 ния 13 формируется сигнал, если П з "(ф в, противном| случае (т. е. кот° д

l.— да П31 > pl < - ) сигнал на выходе блока сравнения отсутствует. Выход блока сравнения 13 соединен со счетным входом триггеpG. 1 7 ° а его выходы управляют элементами

< Я" 15 и 16, тактируемыми одиночньп и импульсами генератора 23 тактов и контрольных обрашенчй. Элементы И 15 и 16 управляют соответственно входами сложения и вычитания реверсивного счетчика 18, задаюmего через преобразователь код-напряжение

19 сигнал управления токами выборки адресного блока упрантения 3 (шина 27). Все тактовые цепи блока адаптации 7 пи гаются re

P нератором 23 тактов и контроль ых обриаений (провода 28 и 29), Сигнал установки в исходное состояние формируется в блоке : режима 25 (на чертеже uemr установки в исходное состояние не показаны). Контрольные циклы адаптации продолжаются до тех пор,,(- 1 пока не окажется, что () " g д > - или пока Не пройдет .- "- KoHTpoJIhHûõ циклов.

В первом случае производится изменение

1 токов выборки на один шаг в обратном направлении и перевод устройства блоком режима 25 в режим "работа". Во втором случае возможны две ситуации: если хотя бы в од. т -1 ном иэ 2 контрольных циклов блок сравнения 13 фиксировал несовпадение отношений сигнал/помеха то блок режима 25 пере водит 3У в режим рабсты; если при всех е-1

2 контрольных обращениях отношение

Д ) "= c,ongt (где 1< i <2 ), то производится возврат токов выборки к первоначальному значению и подача FtoBb)x контрольных циклов обращений с изменением токов вы.борки в противоположном направлении до тех пор. пока не будет найден максимум П м ц .

m-4

Гели и здесь при 2 контрольных циклах отношение (i > " = con sg, то блок режима 25 (по команде с блока сравнения

13) переводит схему 3У в режим работа"

Количество контрольных циклов обращений может быть различным и определяетсц тем, насколько начальное значение токов выборки удалено от оптимального. Макси1 мальное количество контрольных циклов адаптации равно всем возможным комбинациям реверсивного счетчика 18, т. е. 2

47484 ) ; Числа разрядов преобразования и«. в блоке Предмет изобретения

)адаптации 7 определяет точность установки настраиваемого параметра. Практически впол- 3апом««««а«с«цее устройство, со; ержашее нане достаточно иметь ««1 =4-,5, так как в копитель, соединенный с 6 «оком синхронизаfsTw$ случае TOIHocTb устаьовки ToKoB BM- 5 ции, выход которого соедииен с адресным б борки на максимум отношения сигнал/Ho.- блоком ч«равлепия, блок записи-воспроизвемеха составит (9-4,5) 7о.,дения, соединенный с накопителем и блоком

Таким образом, перед началом работы, . синхронизации, о т л и ч а ю ш е е я ,а затем периодически блок управления 4 тем, что, с целью повышения надежности, в настраивается на максимум отношения сиг- ® устройство введены дополнительный блок син нал/помеха для любых внешних условий раба» хронизации, cocTowM из генератора та«ртов ты. Однако длЯ Различных внешних Условий и контрольь«х обращений, счетчика контрольМо«Ют потребоватьсЯ Раэли«ный опти «ал«ный ««ь«х обрашений и ! ,perm ра оть усил"телей с""ть ния к 1ции, содержащий усилитель воспроизведения, ПР изв д "и 6. (й т ь"о 15 преобразователь амплитуда-код регистр де1

I оптимальное значечие порога дискРиминации лителя, блок деления, буферный регистр, р 3 + o /g 1 блок сравнения, триггер, элемент ИЛИ, два

"A оо 2 . элемента ii, реверсивный счетчик, два премож-"т 6« -«т Различи"м в зависимост««от обраэователя код-напряжение, сумматор,при" " ею"«« х местo j ых внеш«ц«х Успев«" N о чем вход "обрашенне" запоминающего устройПОэтомУ при Раб те с Фиксир ванным эначе- ства соединен с входом блока режима, выхо нием порога E Iiqz область Ра отоспособности "BI которого подключены к входу основного орраничена возможностью сбоев при таких 6;о а с« ipонизации, входу генератора так п«ых внешних jjclioBHHx, когда опти; й««ь гов и оН рольнь«х обращений H B oäó адрес ное значение поРога Е сильно отличает-25 -H» o бло.а управ ения, выходы генератора пЧ, соединены с входом счетчика контрольных икси ованного значения Е этому для дальнейшего расширения области рВ«То«о««осТН 3»eo6«AHMo ««epee HB 6 дополнительного разряда накопителя через выбоРки адРесного блока Управленин 4, но Ж . о в н« с е инеи и поРог дискриминации Усилителей воспроиз- 1» = а в т е а ит да код 6 ока адапта ведения в разрядном блоке записи-воспро цни, выходы преобразователя амплитуда-код ,подключены к входам ;блока деления и реблока адаптации 7 на оптимальное значение гистра делителя; выход блока деления соединен c oiiHHM HG Bxogoe блока сравнения H входом буферного Регистра, выход которого соответственно в преобразователе амплиту- :подключен к другому входу блока сравнения, . выход кстого подключен к первому входу

Умм" P 2I «PMУ- ) - - ход элемента Цдка, д угой вход кото ого соедии и щ

ЧеРез преобразователь код "априже"не (нен с выходом блока режима, а выход эле, мента ИЛИ соединен со счетным входом дискриминации (или жзфф цие««то усиления)

Усилителей воспРоизведениЯ РазРЯдного бло первым входам элементов 8» BTopbie вхо ка записи-воспроизведениЯ 6 (шина 30). ды которых соединены с выходом генератора

Следовательно для гпобых вьешних Условий, ;дополнительного блока синхронизации а

1 работы (температуры, напряже««ий пита -«ия выходы элементов И соединены со входами накопителя) Реа««изуеT« I наилу «ш«й Ре- саоТВеТсТВеННо сложения и вычитания жим воспроизведения информации, TBK KBK . Реверсивного счетчика выход реверсивного

Ф обеспечивается максимальное отношение . счетчика через первый преобразователь сигнал/пэмеха, а порог дискриминации в-"-е"-, код-напряжение соединен с управляющим да выбирается посередине между полезньп «, входом адресного блока управления сигналом и помехой (формула 1). Потому входы сумматора соединены с с выхопредложенное устройство позволяет полно- дами преобраэоват ля амплитуда- о стью использовать физические возможности регистра делителя, выходы сумматора соеэлементов памяти, обеспечивая максималь- динены со входами второго преобразовате55 но достижимую область работоспособности ля код-напряжение, выход которого подклн>ЗУ. чен к входу бл ка записи-воспроизведения,