Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

.1

О П И С А Н И Е < ч47484У

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик (61) Дополнительное к авт. свид-ву 226681 (22) Заявлено 25.07.72 (21) 1816295/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 25.06.75. Бюллетень № 23

Дата опубликования описания 21.10.75 (51) Ч. Кл. G 11с 11/06

Тосударствеииый комитет

Совета Министров СССР по делам изобретекмй и открытий (53) УДК 681.325.66 (088.8) (72) Авторы изобретения

Г. А. Петров и В. В. Спиридонов (71) Заявитель Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть, использовано в устройствах для хранения дискретной информации.

Из основного авт. св. № 226681 известно логическое;запоминающее устройство (ЗУ) на тороидальных сердечниках с прямоугольной петлей гистерезиса (ППГ), садержащее на коiTIHTeJIb C чHC O BblMH JIHHeÉKамH, iHMelOIgn>ifH и ,нейные шины записи и считывания и общие разрядные шины записи, считывания и чтения, усилители чтения, разрядные и адресные формирователи записи и считывания, регистры слова, регенерации и признаков обращения,,разрядные вентили, элементы ИЛИ, вентили регенерации, адресные вентили, управляющие элементы ИЛИ и шины управления.

Известное логическое ЗУ характеризуется невозможностью |выполнения в нем сложных логических операций.над матрицами двоичных символов (операций транспонирования и логического умножения).

Цель изобретения — расширение области применения ЗУ.

Для этого, предлагаемое устройство содержит разрядный распределитель, вентили маскирования, разрядно-адресные вентили н ад:ресные элементы ИЛИ,,причем выходы разрядного распределителя соединены с сигнальными входами вентилей маскирования, к управляющим входам которых цтодключена соответствующая шина управления, а выходы вентилей маскирования подключены к элементам ИЛИ, сигнальные входы разрядно-адресных вентилей соединены с прямыми выходамп б триггеров регистра регенерации, управляющие входы разрядно-адресных вентилей подключены к соответствующей шине управления, а выходы этих вентилей через адресные элемеЛтьт

ИЛИ соединены с единичными входами триг 0 геров регистра признаков обращения.

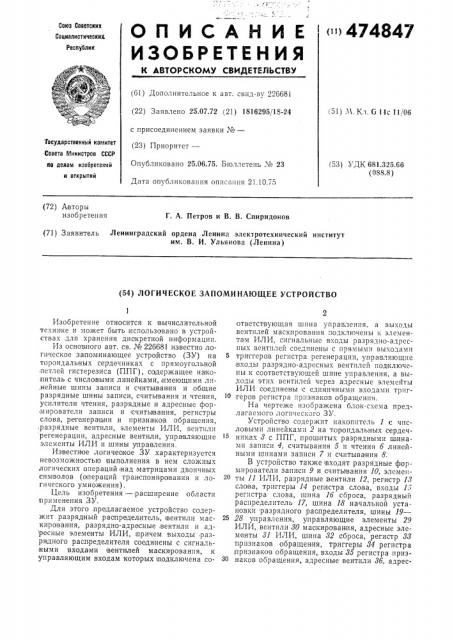

На чертеже изображена блок-схема предлагаемого логического ЗУ.

Устройство содержит накопитель 1 с числовыми линейками 2 на торопдальных сердечниках 8 с ППГ, прошитых разрядными шинами записи 4, считывания 5 и чтения б линейными шинами записи 7 и считывания 8.

В устройство также входят разрядные формирователи записи 9 и считывания 10, элементы 11 ИЛИ, разрядные, вентили 12, регистр 18 слова, триггеры 14 регистра слова, входы 1» регистра слова, шина 1б,сороса, разрядный распределитель 17, шина 18 начальной установки разрядного распределителя, шины 19—

25 28 управления, управляющие элементы 29

ИЛИ, вентили 80 маскирования, адресные элементы 81 ИЛИ, шина 82 сброса, регистр 88 признаков обращения, триггеры 84 регистра тпризнаков обращения, входы 85 регистра призЗО иаков обращения, адресные вентили 8б, адрес474847 рых связаны с прямыми выходами тригILpoB

48 регистра 42 регенерации, находящихся в единичном состоянии, появляются выходные сигналы, которые через и ресные элементы 31

ИЛИ поступают на входы установки в «1» соответствующих триггеров 84 регистра 88 признаков обращения.

Ч е т в е р т ы и т а к т — заикнись k-ой строки матрицы А в /г-ый разряд первых п числовых линеек 2 накапителя 1.

Для этого подается сигнал на управляющую шину 26, поступающий через вентиль 80 маскирования, сигнальный вход которого связан с возбужденным выходом разрядного распределителя 17, и элемент 11 ИЛИ на запуск соответствующего разрядного формирователя

9 записи. Одновременно через управляющий элемент 29 ИЛИ и адресные вентили 86 происходит запуск тех адресных формирователей

88 записи, входы которых через адресные вентили 36 связаны с прямыми выходами триггеров 34 регистра 38 признаков обращения, находящихся в состоянии «1». При этом те сердечники 8 числовых линеек 2,накопителя 1, на:которые воздействуют адресный .и разрядный полутоки, переключаются в состояние «1».

Таким образом, в результате вы полнения этого такта в Й-ом цикле происходит транспонирование k-ой строки матрицы А, т. е. состояние сердечников 8 k-ого разряда первых и числовых линеек 2 соответствует значениям элементов k-ой строки матрицы А.

П я т ы и т а к т — очистка регистра 42 регенерации и регистра 38 признаков обращения.

Для этого подается управляющий сигнал на шины 82, 44 сброса, поступающий на входы установки в «О» триггеров 84 регистра 83 признаков обращения и триггеров 48 регистра 42 регенерации.

Ш е с т о и т а,к т — анализ окончания транспонирования матрицы А, подготовка разрядного распределителя 17 и регистра 38 призHBIKQIB об ращения к следующему .циклу.

В рассмотренном случае квадратных матриц с числом строк и столбцов, равным п, признаком окончания операции транспонирования матрицы А служит наличие сигнала на последнем выходе разрядного раопределителя

17. (В более общем случае этот признак должен быть сформирован в блоке управления).

Для транспонирования очередной строки матрицы А произ водят подготовку к следующему циклу, которая осуществляется установкой в единичное "îñòîÿíèå триггера 84 регистра 38 признаков обращения, соопветспвующего а + -ой числовой линейке 2, где k — номер цикла, посредством подачи сигнала на входы

35 регистра ЗЗ признаков обращения и подачей управляющего импульса на |шину 19, в результате:воздейсгвия которой выходной сигнал разрядного распределителя 17 переходит с k-ого на (k + 1)-ый, выхад. При наличии сигнала окончания транспониравания матрицы А (сигнал на п-ом выходе разрядного,распределителя 17) подается упрагляющпй импульс на шину IS начальной установки разрядного распределителя 17.

Таким образом, IIo окончаниии первого этапа выполнения операции логического умножения булевскпх матриц А и В, в первых 12 числовых линейках 2 накапителя 1 оказываются записаны строки транспонированной матрицы

А(А "1.

Для выполнения второго этапа освобождают первые п числовых лцнеек:2 накопителя 1, что осуществляется пересылкой м.атрв цы А в те числовые линейки 2 накапителя 1, в котоpbIx первоначально была записана матрица А.

Так как пересылка следует непосредственно за этапом транспонированпя матрицы А, триггеры 84 регистра 83 прпзнаказ обрагцен41я и триггеры 48 региспра 42 регенерации находят=я в нулевом сосгоянаи;,разрядный распределитель 17 — в исходном состоянии (возбужден первый выход), а сердечники 3 с а1-ой по а „-ую числовых линеек 2 включительно — в

:остояшп1 «О». Псресылка матрицы А производится за п циклов (в k-ом цикле пересылается k-ая строка матрицы А )., каждый из коГ) торых включает в себя следующие такты:

П е р в ы и т а к т — установка адреса очередной строки матрвцы А .

Для этого на вхады 35 регистра признаков обращения подается соопветствующий входной сигнал, который устанавливает k-ый триггер

34 регистра 38 признаков обращения в состояние «1».

В т о р о и т а к т — считывание k-ой строки матрицы А на регистре 42 регенерацви.

Производится аналогично первому такту цикла этапа транспонирования матрицы А посредством подачи сигнала на управляющую штину 24..

Т р е т и и т а к т — очистка регистра 83 признаков обращения.

Для этого подается управляющий сигнал на шину 82 сброса, лоступающий на входы установки в «О» триггеров 34 регистра 33 признаков обращения.

Ч е т ве р т ы и т а к т — установка адреса а -ой числовой линейки 2.

Для этого на входы 35 регистра ЗЗ признакав обращения подается входной сигнал, который устанавливает триггер 84 регистра 33 признаков обращения, соответствующий а -ой числовой линейке 2 накопителя 1, в единичное состояние.

П я т ы и т а к т — запись k-ой строки мат55 рицы А в ад-ую числавую линейку 2 накопителя 1.

Для этого подается сигнал на упра|вляющую шину 27, поступающий через те вентили

45 регенерации, сигнальные входы которых ,подключены к прямым выходам триггеров 43 регистра 42 регенерации, находящихся в состоянии «1», на.выходы элементов 11 ИЛИ, а с выходов последних — на запуск соответствующих разрядных формирователей 9 записи.

Одновременно через управляющий элемент 29

И ИЛИ и адресный вентиль 36, сигнальный вход

474847 ко-oporo овяэапя с прямым гыходом триггера

34 регистра 83 признаков обращения, находящс",:n B со "тоянии «1», происходит запуск с„ответствующего адрь=;ного формирователя 88 за иси. Прп этоМ To ердечники ап-o}t числовой линейки 2 накопигеля .1, на 1(оторы= воз;;сй> езуют адреоный и разрядный полутоки, .:о>(хлючаются в состояние «1». Таким ооразом, в результате выполнения этого такта з

k-ом цикле в ui<-oA числовой линейке 2 окажется записана k-ая строп(а матрч1цы А .

Ш е с то и r а к т — очистка регистра 88 .;:.,мзнакоз .обращения, очистка репистра 42 регенерации, анализ окончания пер:ылки

viã -пины А .

Для этого подается управляющий сигнал на шины 82 и 44 сброса, поступающий íà входы установки:в «О» трпггероз 84 регистра 83 признаков обращения и триггеров 43 регистра

42 регенерации. Одновременно анализируется пгризнак окончания пересылки матрицы А (в

;;annoì случае — наличие сигнала;на последnем выходе разрядного распределителя 17), в отсутствие, которого подается управляющий импульс на шину !9, переводящий выходной с:гнал разрядного распределителя 17 с Iг-ого на (lг + 1)-ый выход. При налички признака окончания пересылки матрицы А,iiojàå Ton управляющий сигнал на шину И начальной уста невки разряцното расп реде>тит яя 17.

Таким образом, по окончании перссылк:< матрицы А последняя оказывается записанной в числовых линейках 2 накопителя 1 с а -ой по а,-ую числовую линейку 2,вкл1очательно, сердечники 8 первых и числовых линеек 2 накопителя 1 находятся;в состоянии «0», разрядный распределитель 17 — в исходном состоянии (возбужден первый, выход), а триггеры

34 регистра 38 призна кон обраще1пяя;и триггеры 48 регистра 42 регенерации установлены .в нулевое состояние. С этого момента начинается второй этап вьпполнения операции логического умножения булевской матрицы А на булсвскую матрицу В, осуществляемый также за и циклов, каждый пяз которых, включает 9 себя следующие девять тактов:

П е p:â ы и т а к т — установка адреса а,-ой гисловой линейки 2.

Вьпполняется так же, как и четвертый такт цикла пересылки матрицы А при подаче на входы 85 регистра 88 признаков обращения соответствующего. сигнала.

В т о р о и т а к т — считывание k-ой строки матрицы А на регистр 42 регенерации.

Выполняется так же, как и первый такт цикла этапа транспонирования матрицы А при подаче оипналов на управляющую шину

24 и шину 40 строба.

Т р ет и и т а.кт — очистка реги тра 88 призиа коз обращения.

Выполняется так же, как и второй такт цикла этапа трацспонирования матрицы А при подаче управляющего сигнала на шину

82 сброса.

Ч е т в е р т ы и т а к т — — пересылка содержимого регистра 42 регенерации на регистр

88 признаков обращения.

Выполняется так же, как и трет и такт цикла этапа трапспонирования матрицы А при подаче сигнала на управляющую шину

89.

П я т ы и т а к т — очистка регистра 42 регенерации.

Для этого подается управляющий сигнал на шину 44 сброса, поступающий на входы у становки в «0» тр иггвров 48 .реги "тра 42 регенерации.

Ш е с т о и т а к т — установка адреса Р -ой числовой линейки 2. Для этого на входы 85 регистра 88 признаков обращения подается входной сигнал, который устанавливает триггер 84 регистра 88 признаков обращения, соответствующий Ру-ой числовой линейке 2 накопителя 1, в единичное состояние.

С е д ь м о и т à и(т — считьпзаиие k-ой строки матрицы В на регистр 42 регенерации.

Выполняется так же, как и первый такт цикла этапа тра с матрицы А, с той лишь разницей, что управляющие сигналы .подаются на шину 25 и также на шину

40 строба. Это позволяет не осуществлять запуск адресных формирователей 87 считывания тех перовых и числовых линеек 2 накопителя 1, которым соответствуют триггеры 84 регистра 83 признаков обращения, находящиеся в единичном состоянии, что имеет место при ра венстве единице соответствующих элементов

k-ой строки матрицы А, записанной на регистр 88 признаков обращения з четвертом такте данного цикла.

Таким образом, в результате первых семи тактов k-oio цикла второго этапа выполнения операции логического умножения булевских матриц А и В состояние i-ого триггера 84 регистра 88 признаков обращения будет соответствовать значению элемента ап, матрицы

А, равного элементу а „матрицы А, а состояние триггера 48 /-oro разряда регистра 42 регенерации — значению элемента Ь ; матрицы В

В о с ь,м о и т а к т — получение попарных коныанкций между всеми элементами k-ой строки матрицы А и всеми элементами k-ой строки матрицы В.

Для этого подается сигнал на управляющую шину 27, поступающий через те вентили

45 регенерации, сигнальные входы которых связаны с прямыми выходами триггеров 43 регистра 42 регенерации, находящихся з единичном состоянии, и через схемы 11 ИЛИ на запуск соответствующих разрядных формирователей 9 записи. Одновременно через управляющие элементы 29 ИЛИ и через те адресные вен пили 86, оигнальные входы которых соединены с прямыми выходами триггеров 84, регистра 88 признав(с з обра щения, находяцпихся в со стоянии «1», происходит запуск со ответствующих адресных форми ро ватедей 88 записи. П ри этом в единичное состояние переключаются только те сер474847

5

10 !

25

Зо

40 дечники 8 числовых линеек 2 накопителя 1, находив неся в состоянии «0», на которые воздействуют адресный и разрядный лолутоки, л те:cp ie-гн»ки, которые находились в состоя»: .. >>, нс засгенят ето. Так как 1-ый адрес»»:й фор м» рователь 88 записи возбуждается,з .;ланом такте /г-ого цикла,в том н только 3 том случае, когда элемент а;, гматрицы А (равный элементу а „матрггцы A ) равен единице, а разрядный формирователь

9 записи j-oro раз ряда возбуждается в данном такте А-oro цикла в том и только в том случае, когда элемент Ь „матрицы В также равен единице,,сигнал, переключения з единичное состояние сердечника 8 j-ого разряда г-ой ч исловой линейки 2 накопителя 1 (т. е. одновременное:возбуждение г-ого адрс=ного фор мирователя 88 записи и разряд|ного формирователя 9 записи 1-ого разряда) будет соответствовать значению конъюнкции аи,,бд„..

К роме того, в результате выполнен,:. я данного такта в k-ом цикле k-ая строка матрицы

В,будет вооста новлена в Pr,-ой число«вой линейке 2, откуда она была считана в седьмом такте этого цикла, так как триггер 84 регистра 88 признаков обращения, соответствующ.ш

Pq-ой числовой линейке 2 накопителя 1,,пpи выполнен r» этого (восьмого) такта находится в состоянии «1».

Д е в я т ы и т а к т — очистка регистра

88 признаков об ращения, оч:гстка регистра

42 регенерациями, а нализ окончания, операции логического умножевия булевской матрицы

А на булевскую матрицу В.

Вьгполняется так же, как и шестой такт цггкла пересыл ки матрицы А посредством подач>и управляющих аигна>тов на шины 82 и 44 сброса и, при,наличии приз нлка окончания опера ции (в данном случае — сигнала на .последнем выходе разрядного расзределителя 17), на шину 18 начальной установки разрядного расп ределлгтеля 17, а в его отсутствие — яа управляющую шину 19.

Тагким ооразом, в,результате зыполгне:-шя второго этапа операции логического умножения булеBclKOH матрицы А на булевскую матрицу В состоя ние сердечников 8 j-oro разряда i-ой числовой линейки 2 накопителя 1

Л будет соответствовать значению i а;,br„, lг =! т. е. в первых 12 числовых линейках 2 накопителя 1 будут записаны строки некоторой булввской матрицы С, являющей".ÿ,,по оп ределению, результатом выполнения операции логического умножения булевской матрицы А на булевскую >матрицу В.

Предмет изобретения

Логическое запоминающее у стройстзо rrn авт. св. № 226681, отличающееся тем, что, с целью расширения области чтрименения, оно содержит разрядныи;распределитель, вент гли маскгировання, разрядно-адресные вентили и адресные элементы ИЛИ, выходы рлзрядного распределителя соедчгнсны с сигнальны ми входами вентилей маскирования, к у.»ра вляющим входам которых подключена соответствующая шина управлсн и, л выходьг вентилей мас1кирования подключены IK элементам ИЛИ, сигнальные входы разрядноадресных вентилейг соединены с прямьгми выходами триггеров регистра дегенерации, управляющие входы разрядно-адресных вентилей подключены к соответствующей шине управления, а выходы этих вентилей черо адресные элементы ИЛИ совд.ше ы с сдин ичныхги входами триггеров рег»стрл признаков обращения.

474847!

Редактор Г. Иванова

Корректор И. Снмкина

Заказ 837/1272 Изд. ¹ 806 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, Ж-35, Раушская наб., д. 4/о

Тип. Харьк. фил. пред. «Патент»

35 j

° > (Составитель Г. Петров

Тсхред Е. Подурушпна

+г ! и! !