Реверсивный регистр сдвига

Иллюстрации

Показать всеРеферат

О П И С А Н И Е «!)474853

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саиз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-гу— (22) Заявлено 05.01.71 (21) 1607642/18-24 (51) М. Кл. G 11c 19)00 с присоединением заявки— (32) Приоритет—

Опубликовано 25.06.75. Бюллетень М 23

Дата опубликования описания 21.10. 5

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий, 53) УДК 621.374.32 (088.8) ! ( (72) Лвторы изобретения

И. М. Лазер, А. И. Кулешов и П. И. Овсищep (71) Заявитель (54) РЕВЕРСИВИЫЙ РЕГИСТР СДВИГА

Изобретение относится к вычислительной технике и дискретной автоматике и предназначено для операций прямого и обратного сдвига двоичных чисел.

Известен реверсивный регистр сдвига, построенный на основе триггеров типа D, каждый разряд которого состоит из трех RS-триггеров — одного памяти и двух коммутационных, причем RS-триггер памяти имеет одно единичное и два нулевых плеча, управляемых сигналами реверса.

Однако наличие в известном реверсивном регистре критических состязаний логических элементов может привести к сбоям в работе регистра.

Цель изобретения — повышение помехоустойчивости устройства.

Достигается это тем, что предлагаемое устройство содержит в каждом разряде триггер памяти, первый и второй коммутационные триггеры, выполненные на элементах И—

НЕ, и отличается от известного тем, что каждый !K!ofvl!мутацион|ный триггер содержит дополнительный элемент И вЂ” НЕ, образующий второе нулевое плечо коммутационного триггер;а с дополнительным нулевым IBblõîäîì и нулевыми входами. Единичный выход первого коммутационного триггера соединен с одним из нулевых входов второго коммутационного триггера предыдущего разряда регистра и с одним из дополнительных нулевых входов второго коммутационного триггера последующего разряда. Нулевой и дополнительный нулевой выходы первого коммутационного триг5 гера соединены с единичными входами триггера памяти, единичный выход второго коммутационного триггера соединен с нулевым входом первого коммутационного триггера предыдущего раз ряда и с дополнительным

10 нулевым входом первого коммутационного триггера последующего разряда, нулевой выход второго коммутационного триггера соединен с нулевым входом триггера памяти и с одним из нулевых входов второго коммутационного триггера предыдущего разряда. Дополнительный нулевой выход второго коммутационного триггера соединен с одним из нулевых входов триггера памяти и с одним из дополнительных нулевых входов второго ком2О мутационного триггера последующего разряда. Нулевой вход первого коммутационного триггера соединен с единичным выходом второго коммутационного триггера последующего разряда, дополнительный нулевой вход

25 первого коммутационного триггера соединен с единичным выходом второго коммутационного триггера предыдущего разряда, нулевые входы второго коммутационного григгора соединены с нулевым и с единичным выходаЗо ми соответственно второго и первого комму474853 тацио;шых триггеров последующего разряда.

Дополнительные нулевые входы второго коммутационного триггера соединены с дополнительным нулевым и с единичным выходами соответственно второго и первого коммутационных триггеров предыдущего разряда, один из нулевых входов каждого из коммутацио.шых триггеров каждого из разрядов регистра соединен с шиной сигнала «Савиг влево», а один из дополнительных нулевых входов тех же триггеров соединен с шиной сигнала «Сдвиг вправо».

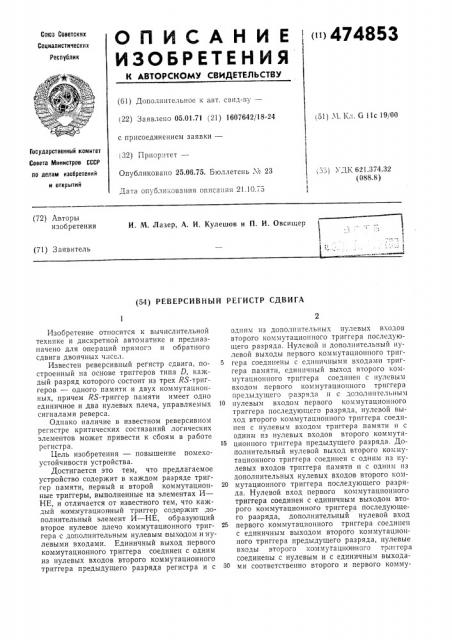

На фиг. 1 приведена схема трех разрядов л стройот ва; на фиг. 2 приведены временные диаграммы, иллюстрирующие функционирсва ние устройства.

Каждый разряд устройства содержит триггер памяти (типа Л, S) на элементах И вЂ” НЕ (и 2, первый и второй коммутационные триггеры на элементах И вЂ” НЕ 8 — 5 и б — 8 соответственно, причем элементы 8, 8 образуют единичные плечи этих триггеров, элементы

4 7— — основные нулевые плечи, элементы

5, б — дополнительные нулевые плечи с соответствующими дополнительными нулевыми входами и выходами.

Нулевые входы каждого коммутационного триггера каждого разряда соединены с шиной 9 «Сдвиг влево», а дополнительные нулевыс входы тех же триггеров — с шиной 10 сигнала «Сдвиг вправо». Нулевые входы и дополнительные нулевые входы коммутациоп1 ых триггеров соединены с шиной 11 тактовых импульсов. По шине 12 на дополпительныи нулевои вход первого коммутационного триггера первого разряда подается прямой код входной информации при сдвиге вправо.

Инверсный код входной информации при сдвиге вправо подается на дополнительные пулевые входы второго коммутационного триггера первого разряда по шинам 18 и 14.

Прямой код выходной информации при сдвиге вправо подается с единичного выхода второго коммутационного триггера последнего разряда па выход 15. Инверсный код той же информации подается на выходы 1б и 17 с едипичного выхода первого и дополнительного нулевого выхода второго коммутацнонпых триггеров того же разряда.

По шине 18 а нулевой вход первого коммутационпого триггера последнего разряда подается прямой код входной информации при сдвиге влево; инверсный код той же информации подается по шинам 19 и 20 па нулевые входы второго коммутационного триггера того же разряда.

Прямой код выходной информации при сдвиге влево подается с единичного выхода второго коммутационного триггера первого разряда на выход 21; инверсный код той же информации подается на выходы 22 и 28 с единичного выхода первого и нулевого выхода второго коммутационных триггеров первого разряда.

Подключение выходов устройства к .соответствующим входным информационныл1 шинам позволяет реализовать различные кольцевые счетчики. Например, при подключении выхода 15 к шине 12, а выходов 1б и 17 соот5 ветственно к цп1нам 18 и 14 реализуется кольцевой счетчик с циклическим кодированием (".о сдвитом информаиии вправо) .

При сдвиге информации вправо во всех разрядах регистра включены дополнительные

10 нулевые плечи коммутационных триггеров, а основные нулевые плечи выключены. При сдвиге информации влево включаются основные нулевые плечи коммутационных триггеров, а дополнительные выключаются. Связи между разрядами регистра обеспечивают управление переключением каждого разряда регистра при помощи информации от соответствующего соседнего разряда, причем эта и формация может изменяться только после

20 окончания тактового импульса. Этот алгоритм работы исключает критические состязания логических элементов различных разрядов. Сам же разряд регистра построен на основ- несимметричного триггера типа Т, который не

25 содержит критических состязаний логических элементов. Учитывая, что управляющая информация не изменяется в момент тактового воздействия, отпадает необходимость во внутренних блокировочных связях между комму30

0 тационными триггерами внутри каждого разряда регистра, Регистр работает без сбоев при произвольных разбросах времени задержки сигналов в логических элементах.

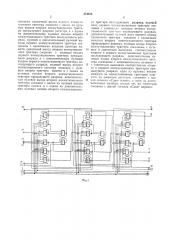

35 Временные диаграммы иллюстрируют последовательность продвижения двух логических единиц через три разряда регистра вправо и влево. Номера временных диаграмм соответствуют нумерации элементов и шин

40 устройства на фиг. 1. Индексы I, II, III указывают на принадлежность элементов И вЂ” НЕ

1/8 первому, второму и третьему разрядам устройства (слева направо на фиг. 1).

Схема устройства может быть реализована

45 па элементах ИЛИ вЂ” НЕ без изменения связей между элементами.

Предмет изобретения

50 Реверсивный регистр сдвига, содержащий в каждом разряде триггер памяти, первый и второй коммутационные триггеры, выполненные на элементах И вЂ” НЕ, единичный выход триггера памяти соединен с единичным вхо55 дом первого коммутационного триггера, единичный выхщ которого соединен с единичным входом второго коммутационного триггера, один из нулевых входов каждого коммутационного триггера соединен с шиной тактовых импульсов, отличающийся тем, что, с целью повышения помехоустойчивости, каждыми коммутационный триггер содержит дополнительный элемент И вЂ” НЕ, образующий второе нулевое плечо коммутационного триггера с до65 полнительным нулевым выходом и нулевыми

474853 входами, единичный выход первого коммутационного триггера соединен с одним из нулевых входов второго коммутационного триггера предыдущего разряда регистра и с одним из дополнительных нулевых входов второго коммутационного триггера последующего разряда, нулевой и дополнительный нулевой выходы первого коммутационного триггера соединены с единичными входами триггера памяти, единичный выход второго коммутационного триггера соединен с нулевым входом первого коммутационного триггера предыдущего разряда и с дополнительным нулевым входом первого коммутационного триггера последующего разряда, нулевой выход второго коммутационного триггера соединен с нулевым входом триггера памяти и с одним из нулевых входов второго коммутационного триггера предыдущего разряда, дополнительный нулевой выход второго коммутационного триггера соединен с одним из нулевых входов триггера памяти и с одним из дополнительпых нулевых входов второго коммутационного триггера последующего разряда, нулевой вход первого коммутационного триггера соединен с единич: ым выходом второго коммутационного триггсра последующего разряда, дополнительный нулевой:вход первого комму тациопного триггера соединен с единичным выходом второго коммутационного триггера предыдущего разряда, нулевые входы второго коммутационного триггера соединены с нуле1О вым и единичным выходами соответственно второго и первого коммутационных триггеров последующего разряда, дополнительные нулевые входы второго коммутационного триггера соединены с дополнительным пулевым и

15 с единичным выходами соответственно второго и первого коммутационных триггеров предыдущего разряда, один пз нулевых входов каждого из коммутационных триггеров каждого из разрядов, регистра соединен с ши20 ной оипнала «Сдвиг влево», а один из дополнительных нулевых входов тех же тритгеров соединен с шиной сигнала «Сдвиг вправо».

Фиг. 2

Редактор Е. Гончар

Заказ 837/1272 Изд. № 806 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»

2х

/Д

6g

-"m ба

7д

1щ

Рд з в, 1879 с0

Составитель В. Игнатущенко

Техред Е. Подурушина Корректор В. Гутман