Двухтактный счетный триггер

Иллюстрации

Показать всеРеферат

O ll H C A H H E

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 4749 l2

C0I03 Советских

Сациалистичвских

Республик (61) Зависимое от авт; свидетельства (51) М. Кл. Н 03k 3/28 .

Н 03k 21/00 (22) Заявлено 04.01.73 (21) 1869654/26-21 с присоединением заявки 4

Государственный комитет

Совета Министров СССР по долам изобретений и открытий (32) Приоритет (53) УДК 621.377.32 (088.8) Опубликовано 25.06.75. Бюллетень М 23

Дата опубликования описания 10.11.75 (72) Авторы изобретения

Л. А. Сулима, В. И. Редченко, Г. А. Кузьмин, В. М. Миролюбский и В. В. Куванов (71) Заявитель (54) ДВУХТАКТНЫЙ СЧЕТНЫЙ ТРИГГЕР

Изобретение относится к импульсной технике.

Известен двухтактный триггер, содержащий триггер памяти с раздельными входами, буферный триггер с раздельными входами и ячейки И вЂ” НЕ, выходы первых двух из которых подсоединены к единичному и нулевому входам триггера памяти соответственно, а первые входы этих ячеек И вЂ” НЕ объединены и подключены к второй шине тактовых импульсов, а выходы триггера памяти подключены через вторые ячейки И вЂ” НЕ к единичному и нулевому входам буферного триггера соответственно, подключенного своими выходами к вторым входам первых ячеек И вЂ” НЕ соответственно, причем вторые входы вторых ячеек И вЂ” HE соединены с первой шиной тактовых импульсов.

Целью изобретения является повышение помехозащищенности.

Для этого в триггер введены выходной триггер с раздельными входами, выходные ячейки

И вЂ” НЕ и инвертор, выход которого подсоединен к объединенным первым входам выходных ячеек И вЂ” НЕ, а вход — к первой шине тактоВых импульсоВ, причем Выходы ВыхОдных ячеек И вЂ” HE подключены к единичному и нулевому входам выходного триггера соответственно, а вторые входы выходных ячеек

И вЂ” HE соединены с единичным и нулевым выкодами буферного триггера, выходы выходных ячеек И вЂ” HE подключены к объединенным третьим и четвертым входам вторых ячеек И вЂ” НЕ соответственно.

Изобретение пояснено чертежами.

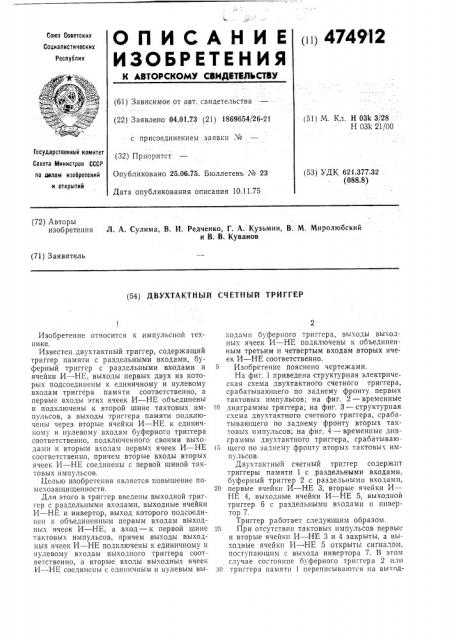

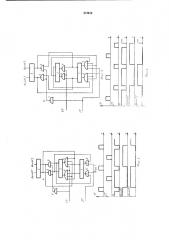

На фиг. 1 приведена структурная электрическая схема двухтактного счетного триггера, срабатывающего по заднему фронту первых тактовых импульсов; на фиг. 2 — временные

)О диаграммы триггера; на фиг. 3 — структурная схема двухтактного счетного триггера, срабатывающего по заднему фронту вторых тактовых импульсов; на фиг. 4 — временные диаграммы двухтактного триггера, срабатываюI5 щего по заднему фронту вторых тактовых импульсов.

Двухтактный счетный триггер содержит триггеры памяти 1 с раздельными входами, буферный триггер 2 с раздельными входами, 2О первые ячейки И вЂ” HE 3, вторые ячейки И—

НЕ 4, выходные ячейки И вЂ” НЕ 5, выходной триггер 6 с раздельными входамц н пнвертор 7.

Триггер работает следующим образом.

25 При отсутствии тактовых импульсов первые и вторые ячейки И вЂ” HE 3 и 4 закрыты, а выходные ячейки И вЂ” НЕ 5 открыты сигналом, поступающим с выхода инвертора 7. В этом случае состояние буферного триггера 2 нли зо триггера памяти 1 переписываются на выход474912 ной триггер 6 с раздельными входами. Перезапись информации на триггеры в данном случае и в дальнейшем производится низким уровнем сигнала. В случае необходимости срабатывания по заднему фронту первого гактового импульса 1Т (см. фиг. 1) передний фронт этого импульса через инвертор 7 низким уровнем поступает на первые входы выходных ячеек И вЂ” НЕ 5, отключая буферный триггер 2 от выходного триггера 6. После появления на выходах выходных ячеек И вЂ” HE 5 высоких уровней, т. е. после полного отключения входов выходного триггера 6 от выходов буферного триггера 2, разрешается прохождение сигналов с триггера памяти 1 на оуферный триггер 2.

В это время выходной триггер 6 отключен от оуферного триггера 2 и сохраняет предыдущую информацшо. После окончания первого тактового импульса инвертор 7 вырабатывает высокий уровень, который разрешает прохождение информации через выходные ячейки И вЂ” HE 5 на выходной триггер. Вторые ячейки И†HE 4 после окончания первого тактового импульса 1Т закрываются, отключая триггер памяти 1 от входов буфер ого триггера 2. Второй тактовый импульс 2Т, поступая на входы первых ячеек И вЂ” HE 3, переписывает передним фронтом состояния с выходов буферного триггера 2 на триггер памяти 1. Далее цикл работы повторяется.

При срабатывании по заднему фронту второго тактового импульса 2Т (см. фиг. 3) триггер работает аналогичным образом.

Отличие состоит лишь в том, что запрещение и разрешение перезаписи информации на о

25 зо

35 выходной триггер 6 осуществляется с триггера памяти 1 импульсами, поступающими по шине вторых тактовых импульсов 2Т.

Предмет изобрстени 1

Двухтактный счетный триггер, содержащий триггер с раздельными входами, буферный триггер с раздельными входами и ячейки

И вЂ” HE, выходы первых двух из которых подсоединены к единичному и нулевом входам триггера памяти соответственно, а первые входы этих ячеек И вЂ” HE объединены и подключены к второй шине тактовых импульсов, а выходы триггера памяти через вторые ячейки

И вЂ” HE подключены к единичному и нулевому входам буферного триггера соответственно, подключенного своими выходами к вторым входам первых ячеек И вЂ” НЕ соответственно, причем вторые входы вторых ячеек И вЂ” НГ соединены с первой ппшой тактовых импульсов, отличающийся тем, что, с целью повышения помехозащищенности, в него введены выходной триггер с раздельными входами, выходные ячейки И вЂ” HE и инвертор, выход которого подсоединен к объединенным первым входам выходных ячеек И вЂ” НЕ, а вход — к первой шине тактовых импульсов, причем выходы выходных ячеек И вЂ” НЕ подключены к единичному и нулевому входам выходного триггера соответственно, а вторые входы выходных ячеек И вЂ” НЕ соединены с единичным и нулевым выходами буферного триггера, выходы выходных ячеек И вЂ” НЕ подключены к объединенным третьим и четвертым входам вторых ячеек И вЂ” НЕ соответственно.