Адаптивный временной дискретизатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< и 474935

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено ) ).06.73 (21) 193)768/) 8-24 с присоединением заявки № 1961556/18-24 (32) Приоритет—

Опубликовано 25.06.75. Бюллетень № 23

Дата опубликования описания 10.02.76 (51) М. Кл. Н 03k )3/16

Государственный комитет

Совета Министров СССР

fi0 делам изобретений и открытий (53) УДК 62).374 (088.8) (72) Авторы изобретения

В. Л. Виттих и В. H. Сабило

Куйбышевский ордена Трудового Красного Знамени авиационный институт им. акад. С. П. Королева (7I ) Заявитель (54) лдлптивныЙ Временной дисКютизлто) Изобретение относится к технике дискретизации непрерывных сигналов.

Известны адаптивные дискретизаторы, измеряющие погрешность равномерного приближения входного непрерывного сигнала прямыми линиями.

Однако использование в качестве приближающих функций только прямых линий значительно снижает точность дискретизирующих устройств при адаптивной временной дискретизации сигналов, описывающих поведение тех демпфирующих систем, для которых процессы накопления и отдачи различных видов энергии носят характер апериодических колебаний. 15

Цель изобретения — повышение точности работы адаптивного временного дискретизатора. Предлагаемый дискретизатор дает возможность измерять погрешность равномерного приближения функцией вида q(t) непре- 20 рывного входного сигнала.

Для этого адаптивный временной дискретизатор содержит блок выборки сигнала, запоминающе-вычитающий блок, два блока суммирования, блок генератора функционально-изменяющегося папряжепия, три блока деления, блок выделения максимального значения поступившего на его вход сигнала, блок выделения минимального значения поступившаго на его вход сигнала, два блока c;). ât ения и блок управления.

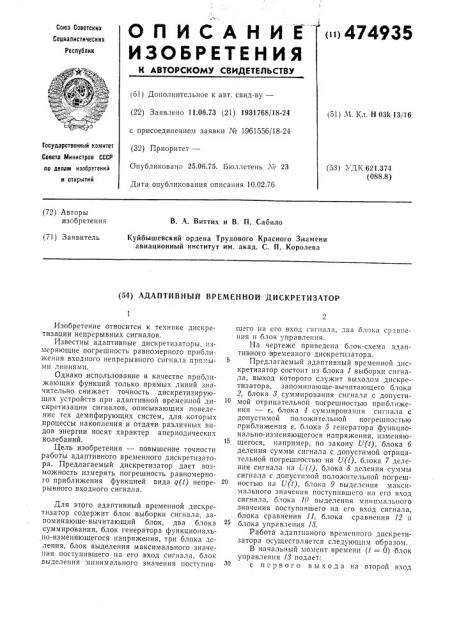

На чертеже приведена блок-схема адаптHBHOIQ временного дискретпзатора.

Предлагаемый адаптивный временной дискретизатор состоит из блока 1 выборки сигнала, выход которого служит выходом дискретизатора, запоминающе-вычптающего блока

2, блока 3 суммирования сигнала с допустимой отрицательной погрешностью приближения — е, блока 4 суммирования сигнала с допустимой положительной погрешностью приближения е, блока 5 генератора функционально-изменяющегося напряжения, изменяющегося, например, по закону l(1), блока 6 деления суммы сигнала с допустимой отрицательной погрешностью на U(t), блока 7 деления сигнала на U(t), блока 8 деления суммы сигнала с допустимой положительной погрешностью на U(t), блока 9 выделения максимального значения поступившего на его вход сигнала, блока 10 выделения минимального значения поступившего на его вход сигнала, блока сравнения 11, блока сравнения 12 и блока управления 13.

Работа адаптивного временного дпскретизатора осуществляется следующим образом.

В начальный момент времени (t = О) блок управления 13 подает: с первого выхода на второй вход

474935,„р 5(1) — 5(0) —.

: (50

65 запоминающе-вычитающего блока 2 импульс, по которому в запоминающе-вычитающем блоке 2 запоминается начальное значение входного сигнала S(0) и начинается вычитание из поступающего сигнала 5(t) значения

5(0); запирается выход запоминающе-вычитающего блока 2, и разность 5(t) — 5(0) не поступает на входы блоков суммирования 8, 4 и первый вход блока деления 7; со второго выхода на вход блока генератора 5 запускающий импульс, и генератор начинает генерировать напряжение

U(t); с четвертого выхода на второй вход блока выделения минимального значения сигнала 10 для запоминания его запоминающим устройством напряжение Ut, с тр етьего выхода на второй вход блока выделения максимального значения сигнала 9 для запоминания его запоминающим устройством напряжение Ug.

Через промежуток времени Л(после начала генерации генератором блока 5 напряжения У(Ц: с пер в ого в ы хода блока генератора 5 посылается отпирающий импульс на третий вход запоминающе-вычитающего блока 2; со второго выхода блока генератора 5 на вторые входы блоков деления б, 7 и

8 начинает поступать напряжение (l(1); блок управления 18 перестает подавать с четвертого выхода на второй вход блока выделения минимального значения сигнала 10 напряжение U, с третьего выхода на второй вход блока выделения максимального значения сигнала 9 напряжение U>.

После отпирания запоминающе-вычитающего блока 2 разность 5(t — 5(0) поступает н а в х о д o:л о к а суммирования 8, где суммируется с отрицательной допустимой погрешностью, С выхода блока суммирования

8 5® — 5(0) — c поступает на первый вход блока деления б. В блоке деления б 5(t)—

5(0) — c делится на напряжение U(t) =1 — e", подаваемое на второй вход блока деления б со второго выхода блока генератора 5. Затем преобразованный сигнал поступает с выхода блока деления б на первый вход блока выделения максимального значения 9, который представляет собой диодный элемент в прямом включении, запирающее напряжение которого равно напряжению запоминающего устройства блока 9. Если максимальное знаS (t) — S (О) — чение напряжения сигнала „равное

1 — е s (1) — s (о) — =-1

), больше напряжения

1 — е" запирания, то диодный элемент отпирается и в запоминающее устройство блока 9 зано S (/) — S (0) — .1 сится р, соответственно

"< 1 — е" увеличивается и напряжение запирания, ста,„Ь (1) — s (0) — «1 новясь равным Р . Зане"< 1 — e"

45 сенное в запоминающее устройство напряжение поступает с выхода блока выделения максимального значения сигнала 9 на второй вход блока сравнения ll; н а п ер в ы и в ход блока деления 7, где

S(t) — S (О) делится на напряжение U(t) =

=1 — е", подаваемое на второй вход блока деления 7 со второго выхода блока генератора

5, затем преобразованный сигнал поступает на первый вход блока сравнения 11 и на второй вход блока сравнения 12; и а в х од бл о к а суммирования 4, где суммируется с положительной допустимой погрешностью. С выхода блока суммирования

4 S(t) — 5(0)+c поступает на первый вход блока деления 8. В блоке деления 8 S(t)—

S(0) +c делится на напряжение U(t) =1 — e", подаваемое на второй вход блока деления 8 со втоpîão выхода блока генератора 5. Затем преобразованный сигнал поступает с выхода блока деления 8 на первый вход блока выделения минимального значения 10, который представляет собой диодный элемент в обратном включении, запирающее напряжение которого равно напряжению запоминающего устройства блока N. Если минимальное знаS (t) — 5 (О) -, — =чение напряжения сигнала

1 — е" !

П1 5(/) — 5(0) —, ° 1 равное „, „, меньше напряЫ <1 1 — е" жения запирания, то диодный элемент отпирается и в запоминающее устройство блока

jpf Is(t) — 5(0) --, =-1

10 заносится,,,,, соответ1 — e" ственно уменьшается и напряжение запира;„1 55 (t) — s (0) -+ -1 ния, становясь равным„, 1 — e"

Занесенное в запоминающее устройство напряжение поступает с выхода блока выделения минимального значения сигнала 10 на первый вход блока сравнения 12.

В блоке сравнения 11 из поступающего с выхода блока выделения максимального значения сигнала 9, вычитаетS (t) — 5 (О) ся сигнал, -, поступающий на пер1 — е" вый вход блока сравнения 11 с выхода блока деления 7.

Начало выполнения неравенства

S(t) — S(0) —.1 S (1) — S(0) с

0 (sup свидетельствует о том, что максимальная положительная погрешность равномерного приближения непрерывного входного сигнала

S(t) функцией q(t) =А(1 — е" ) стала равной или больше допустимой погрешности, т. е. я„,) в.

474935

На выходе блока сравне;п.я 11 в этом случае появляется плюсовое напряжение.

В блоке сравнения 12 из сиги-:.ë",а

S (t) — S(0) 1 — e" поступающего на второй вход блока сравнения

12 с выхода блока деления 7, вычитается

S(t) — 5(0) -, я

1 — е" пост пающее на первый вход блока сравнения 12 с выхода блока выделения минимального значения сигнала

10. Начало выполнения неравенства;

0 S (t) S (0) S(t) S(0) — »

1 — е" свидетельствует о том, что модуль максимальной отрицательной погрешности равномерного приближения непрерывного входного сигнала S(t) функцией q(ti =А (1 — е" ) стал равным или больше допустимой погрешности, т. е. — в„ ) в.

Плюсовое напряжение с выхода или блока сравнения 11, или блока сравнения 12 поступает на первый вход блока выборки сигнала 1, и на его выходе появляется выбранный отсчет дискретизируемого сигна ча; н а вход бл ока управления 13 и с его второго выхода поступает на вход блока генератора 5 импульс, прекращающий генерацию напряжения U(t) =1 — е" и осуществляющий сброс этого напряжения на нуль.

Затем начинается новый цикл дискретизации и все операции повторяются в последовательности, рассмотренной для t= О. Выбор конкретного значения а производится получателем информации по априорным сведениям о демпфирующей системе. Напряжение, генерируемое генератором 5, должно соответствовать выбранному значению а.

Предмет изобретения

Адаптивный временной дискретизатор, содержащий блок сравнения, выход которого соединен с входом блока управления и с псрвым входом блока выборки сигнала, второй вход которого соединен с входом дискретизатора, а выход — с выходом дискретизатора, запоминающе-вычитающий блок, первый вход которого соединен с входом дискрстизатора, а второй вход соединен с первым выходом блока управления, отлпча ощий1ся тем, что, с целью повышения точности работы адаптиг,— ного временного дискретизатора, он содержит два блока суммирования, входы которых соединены с выходом запоминающе-вычитающего блока, генератор функционально-изменяющегося напряжения, вход которого соединен со вторым выходом блока управления, а nepi.ûé выход соединен с третьим входом запоминающе-вычитающего блока, три блока деления, первый вход первого из которых соединен с выходом первого блока суммирования, первый вход второго блока деления соединен с выходом запоминающе-вычитающего блока, а выход соединен с первым входом блока сравнения, первый вход третьего блока деления соединен с выходом второго блока суммирования, вторые входы блоков деления соединены со вторым выходом генератора, блок выделения максимального значения, первый вход которого соединен с выходом первого блока деления, второй вход соединен с третьим выходом блока управления, а выход соединен со вторым входом блока сравнения, блок выделения минимального значения, первый вход которого соединен с выходом третьего блока деления, а второй вход соединен с четвертым выходом блока управления, 4О дополнительный блок сравнения, первый вход которого соединен с выходом блока выделения минимального значения сигнала, второй вход соединен с выходом второго блока деления, а выход соединен с входом блока управ45 ления и первым входом блока выборки сигналаа.

Выкод

Составитель В. Сабило

Тсхред М. Семенов

Корректор В. Гутман

Редактор Е. Гончар

Тип, Харьк. фил. пред. «Патент»

Заказ 1289/1848 Изд. ¹ 812 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5