Моногоканальный коммутатор

Иллюстрации

Показать всеРеферат

О П И C А И И Е 474938

Сонз Саеетских

Сопиаоисткческик

Респу5лик

ИЗОБРЕТЕ Н И Я

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 31.0!.73 (21) 1878267, 26-21 (5! ) М. Кл. Н 03k 17, 02 с присоелине.вием заявки . 4—

Государствеииый комитет

Сооета Мииистров СССР по делам иаооретеиий и открытий (23) Приоритет—

Опубликовано 25.06.74. Бюллетень Хе 23 (53) УДК 621.382 (088.8) З,ата опубликования описания 26.12. 5 (72) Авто р ы изобретения

Б. В. Толмачев, Н. А. Макаров и Ю. Г. Ладыгин (71) Заявитель (54) М НО ГОКА НАЛ Ь Н Ы и КОММУТАТОР макс ааааа. тр ° .

Изобретение отно"ится к импульсной технике и исачользуется .в .иэмер лтельно-информационных вычислительных у "т рой1ствах.

Известны многоканальные коммутаторы, содержащие последовательно соединенные генератор, запрещающий блок, линию задержки, счетчик, г также ступенчатый дешифратор, входы которого соединены через соответствующие предварительные матричные деши фратсры с выходами .счетчика, ключи.

Однако .в известных коммутаторах не исключено появление ложной единицы.

Целью изобретения является и сключение появления ложной единицы.

Для этого в дешифратор введен блок задержки выхода, вход которого соединен с выходом запрещающего блока, а выхол— с соответствующими входами предварительных .матричных двшифр аторов.

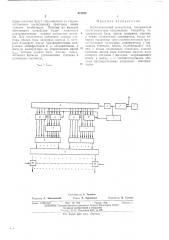

На чертеже приведена структурная элек- 20 прическая схема коммутатора.

Многоканальный коммутатор содержит генератор,прямоугольных импульсов 1, запре.щающий блок 2, линию задержки 8, счетчик

4, блок 5 задержки выхода, предварительные 2о матричные дешиф раторы б, ступенчатый лешифратор, состоящий из первой ступени 7, второй ступени 8 и третьей ступени 9. Выходы обегающего устройства соединены с входами коммутирующих ключей 10, на вторые входы которых посту:IQIoT сигHB;Ibl от латчмков. Импульсы генератора после блока 2 по ступают на вход линии задержки 8 и на вход блока 5. После лин и задержки 3 им пульсы .генератора 1 поступают на вход счетчика 4. Выходы счетчика 4 соединены со сту. пенчатым дешифратором, при помощи которого пропсхолит реализация преобразования двоичного кола в десятичный.

В ступенчатом лешифраторе,вхолныс переменные сначала объединяются,в группы, затем группы объединяются в ступени 7, 8, после чего выходные шины данной ступени объединяются с выходньеми шинами другой ступени, о6разуя третью ступень 9.

Коммутатор работает следующим образом.

Для установления счетчика 4 в устойчивое состояние требуется определенное время, ма кслмальное .значение которого можно найти из формулы: где /ааа.тр — время задержки прохождения сигнала через счетный приггер, и — число триггеров в счетчике.

В связи с этим в процессе передачи единицы переноса новые состояния, первых триг474938

Предмет изобретения

"зал ) /мзкс в ° ° ° o o ° ° o а а à o I

Составитель А. Туляков

Текред 3. Тараненко

Корректор В. Гутман

Редактор Л. Зиньковский

Подписи

Заказ 1109/1647 Изд. № 813 Тираж 902

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

,госква, Ж-35. Раушская наб., д. 4/5

Тип, Харьк. фил. пред. «Патент» горов с гетчпка будут образовывать со старым состоянпсам последующих триггеров новые ложныс комбинации. Поэтому на выходах ооегающсго устройства будут, появляться ,кратковременные ложные логические едпнпЦЫ, ДЛЯ ИСКЛ1ОЧСНИЯ ПОЯВЛЕНИЯ Лажиэй С, ГИнпцы .введен блок задержки выхода з, который блокирует входы предва рительных матричных дешиф раторов б, а, следовательно, и выходы коммутатора на определенное время которое долж Io быть больше макс:Iмыльного времени,установления счетчика в устойчнвос состояенпс, Многоканальный коммутатор, содержащий !

loследэвательно соединенные генератор, за5 прещя1ощпй блок, линию задвржки, счетчик, а также ступенчатый дешифратор, зходы которого соединены чсрсз соответствующие п рсl".г-р.1тсльные матричные дешиф раторы с вы. кодами счетчика, ключи, от.гича ош,ийся тем, что, с целью исключения появления ложной единицы, введен олок задержки выхода, вход которото соединен с выходом запрещающего олока, а выход — с соответству1ощими входами предварительных матричных дешифра15 торов.