Устройство автоматической подстройки частоты

Иллюстрации

Показать всеРеферат

лл 425562

ОГ1ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 01.02.73 (21) 1877881/18-10 с присоединением заявки ¹ (32) Приоритет

Опубликовано 30.06.75. Бюллетень № 24

Дата опубликования описания 15.09.75 (5i) М. Кл. G Olr 23/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.317.761 (088.8) (72) Авторы изобретения

И. М. Вишенчук, А. П. Конопкин и Н. Г. Гитшов

Львовский ордена Ленина политехнический институт (71) Заявитель (54) УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ

ЧАСТОТЫ

Изобретение относится к области электроизмерительной техники и может быть использовано для повышения помехоустойчивости приборов, в частности цифровых вольтметров.

Известны различные системы автоподстройки частоты. Наиболее часто в цифровых вольтметрах используются системы фазовой автоподстройки частоты. Эти системы обладают важным преимуществом перед остальными известными системами: остаточная разность между эталонной и подстраиваемой частотами равна нулю.

Для известного устройства автоматической подстройки частоты характерна нелинейность (девиация мгновенного значения) частоты управляемого генератора в течение интервала измерения, что приводит к нелинейности шкалы цифрового вольтметра. Эта нелинейность вызвана пульсациями выходного напряжения фильтра, возникающими из-за недостаточной величины постоянной времени фильтра. При увеличении постоянной времени пульсации уменьшаются и снижается нелинейность частоты. Однако увеличение постоянной времени фильтра нежелательно, так как при этом снизкается быстродействие системы и значительно сужается полоса схватывания (диапазон подстраиваемых частот).

Цель изобретения — уменьшение нелинейности частоты управляемого генератора без уменьшения зоны схватывания и быстродействия системы автоподстройки частоты.

Это достигается тем, что в схему, представляющую собой замкнутую цепь из фазового детектора, фильтра, управляемого генератора и делителя частоты, включены два параллельных канала, связывающих выход фильтра с входом управляемого генератора. Каждый канал содержит емкость памяти, подключенную через входной ключ к выходу фильтра, а через выходной ключ — к входу управляемого генератора. При этом к выходу делителя частоты подсоединен триггер со счетным входом, прямой выход которого связан с управляющими цепями входного ключа одного канала и выходного ключа другого канала, а инверсный выход триггера связан с управляющими цепями двух остальных ключей.

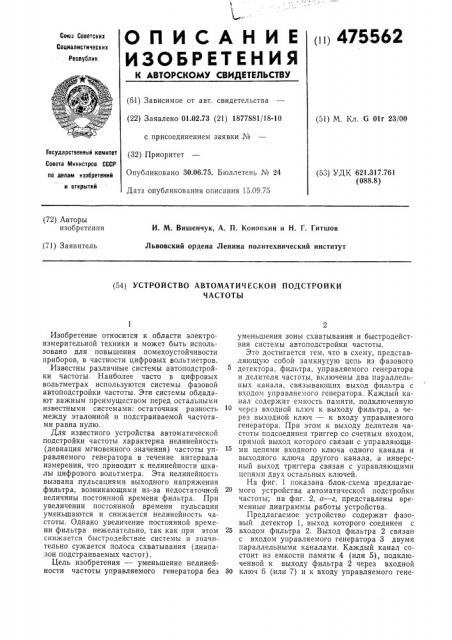

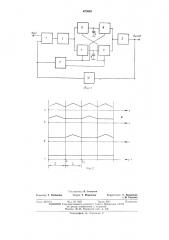

На фиг. 1 показана блок-схема предлагае20 мого устройства автоматической подстройки частоты; на фиг. 2, а — г, представлены временные диаграммы работы устройства.

Предлагаемое устройство содержит фазовый детектор 1, выход которого соединен с

25 входом фильтра 2. Выход фильтра 2 связан с входом управляемого генератора 3 двумя параллельными каналами. Каждый канал состоит из емкости памяти 4 (или 5), подключенной к выходу фильтра 2 через входной

30 ключ 6 (или 7) и к входу управляемого гене475562

10 ратора 3 через выходной ключ 8 (или 9) . Выход управляемого генератора 3 соединен с выходом устройства и через делитель частоты

10 — с одним из входов фазового детектора 1.

Другой вход фазового детектора включен на вход устройства. Кроме того, к выходу делителя частоты подключен триггер 11 со счетным входом, прямой выход которого соединен с управляющими цепями ключей б и 9, а инверсный вход триггера 11 соединен с управляющими цепями ключей 7 и 8.

На входы фазового детектора поступают сигналы двух частот: эталонной (с входа устройства) и подстраиваемой (с выхода делителя частоты 10). Выходной сигнал фазового детектора 1, усредненный фильтром 2, представляет собой функцию разности этих частот. В связи с конечной величиной постоянной времени фильтра 2 его выходное напряжение содержит пульсации, наложенные на постоянную составляющую (фиг. 2, а) . Это напряжение поступает на ключи б и 7. В отрезок времени Т> ключи 6 и 9, например, замкнуты, а 7 и 8 разомкнуты. Тогда напряжение с выхода фильтра 2 через замкнутый ключ 6 проходит на емкость памяти 4, которая следит за этим напряжением и фиксирует его значение в момент времени f> (фиг. 2, 6).

На вход управляемого генератора 3 в этот отрезок времени поступает постоянное напряжение, зафиксированное емкостью памяти 5.

В отрезок времени Т> ключи б и 9 разомкнуты, ключи 7 и 8 замкнуты, и выходное напряжение фильтра 2 в момент времени 1 фиксируется емкостью памяти 5 (фиг. 2, в). В этот же отрезок времени напряжение, зафиксированное емкостью памяти 4 в предыдущий отрезок времени Т>, поступает на вход управляемого генератора 3 (фиг. 2, б).

Таким образом, в любой отрезок времени на вход управляемого генератора подается постоянное напряжение, лишенное пульсаций.

Выходной сигнал управляемого генератор".

40 через делитель 10 частоты подается на входы фазового детектора и триггера 11. Триггер управляет работой ключей 6 9 так, чтобы ключи 6 и 9 работали в противофазе с ключами

7и8.

По сравнению с известным предлагаемое устройство уменьшает нелинейность частоты управляемого генератора в 1000 раз, нс уменьшая при этом полосы схватывания и быстродействия системы.

Предмет изобретения

Устройство автоматической подстройки частоты, содержащее последовательно соединенные фазовый детектор. фильтр, управляемый генератор и делитель частоты, причем выход делителя частоты подключен к второму входу фазового детектора, о т л и ч а ю щ е е с я тем, что, с целью уменьшения нелинейности частоты управляемого генератора, оно снабжено двумя запоминающими устройствами, двумя входными ключами, двумя выходными ключами и триггером, причем первый входной и выходной ключи соединены последовательно, при этом вход первого входного ключа подключен к выходу фильтра, а выход первого выходного ключа — к входу управляемого генератора, второй входной и выходной ключи также соединены последовательно так, что вход второго входного ключа подключен к выходу фильтра и выход второго выходного ключа — к входу управляемого генератора, при этом управляющие входы первого входного и второго выходного ключей, а также второго входного и первого выходного ключей обьединены и подключены соответственно к первому и второму выходам триггера, вход которого подключен к выходу делителя частоты, причем первое и второе запоминающие устройства включены соответственно между выходами первого и второго входных ключей и корпусом устройства.

475562

Составитель В. Степанов

Редактор Т. Рыбалова Техред Т. Миронова Корректоры: С. Болдижар и Н. Учакина

3ака: 2215/11 Изд. ¹ 1555 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раугиская наб., д. 4/5

Типография, пр. Сапунова, 2