Устройство для контроля и диагностики неисправностей двоичных схем

Иллюстрации

Показать всеРеферат

пмтен

<1ц 476564

0 П И С А В- М Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 06.12.72 (21) 1857527/18-24 с присоединением заявки № (51) М. Кл, G 06f 11/00

Совета й1иннстров СССР по делам изобретений и открытий

Опубликовано 05.07.75. Бюллетень № 25

Дата опубликования описания 28.11.75 (53) УДК 681.326(088.8) (72) Авторы изобретения

Т. К. Коробцов и В. В. Павленко

Ждановский металлургический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ДИАГHОСТИКИ

НЕИСПРАВНОСТЕЙ ДВОИЧНЫХ СХЕМ госУдаРственный комитет (32) Приоритет

Изобретение относится к вычислительной технике.

Известны устройства для контроля и диагностики неисправностей двоичных схем, содержащие блок матричной памяти, дешифратор строк, соединенный выходами с горизонтальными шинами записи блока памяти, а входом — с входной клеммой устройства, и выходной регистр блока памяти, соединенный входами с выходами считывания данных блока памяти.

Для нормальной работы известного устройства необходим полный список возможных неисправностей с признаками, сопровождающими их появление. Составление такого списка даже для сравнительно простых схем черезвычайно трудоемко. Эти трудности возрастают пропорционально числу схем или приборов, при контроле данным устройством. Кроме того, вероятно, что в сложной схеме одним и тем же признаком соответствуют различные неисправности.

Целью изобретения является создание устройства для поиска неизвестных неисправностей и локализации их места в двоичных схемах.

С этой целью в него дополнительно введены входной регистр, входы которого подключены ко входам устройства, схемы сравнения. Первый вход первой схемы сравнения соединен со вторым входом второй схемы сравнения, второй — с первым входом третьей схемы, попарно соединенные входы схем сравнения соединены с выходами входного регистра. Выходы

5 схем сравнения соединены с вертикальными шинами записи блока памяти. Вход блока индикации соединен с выходом выходного регистра.

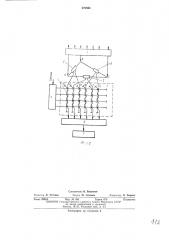

На фиг. 1 изображена блок-схема устройстIO ва; на фиг. 2 — вариант схемы с ферритовой памятью матричного типа и выходным регистром на триггерах (показана схема с тремя выходами, хотя их число может быть любым, число тактов условно равно четырем).

15 Устройство состоит из входного регистра 1, блока сравнения 2, выходы которого соединены с вертикальными шинами матричного блока памяти 3, горизонтальные шины которого соединены с выходами дешифратора строк 4.

Выходы считывания 5 блока памяти соединены с выходным регистром 6, который соединен с блоком индикации 7.

В работе устройства можно выделить два этапа: обучение и собственно диагностику.

25 Обучение производится на исправной схеме, на которую подается выбранная тестовая последовательность операций, при этом сигналы с контро IbHIIx точек запоминаются на входном регистре 1. Выходные сигналы регистра зо поступают на узловые точки блока сравнения

476564, ?, состоящего из схем сравнения, имеющих два входа и два выхода. В случае равенства сигналов на входах сигналы на выходах отсутствуют. Если на одном из входов сигнал равен единице, а на втором — нулю, то возбуждается один из выходов, если наоборот — то второй. Сигналы с выходов блока 2 сравнения (схем сравнения) поступают на вертикальные шины блока памяти 3, на горизонтальные шипы которого поступают сигналы с дешифратора строк 4.

При совпадении этих двух сигналов (токов) перемагничиваются сердечники, которые перед началом работы установлены в исходное состояиие. При перемагничивании сердечников с вь!ходов считывания 5 снимаются сигналы, которые поступают на счетные входы регистра б, состояние которого в каждый момент времени индицирует блок индикации 7. При работе регистр б проводит сложение по модулю два, и по завершении тестовой последовательности в выходном регистре 6 фиксируется код, для которого изготовлена маска.

На этом процесс обучения заканчивается.

На этапе диагностики повторяется процесс обучения, а решение об исправности схемы и локализации неисправного элемента выносится по результатам сравнения кодов маски и блока индикации 7.

Неправильная работа контролируемой схемы устанавливается в случае несовпадения кода маски с кодом, зафиксированным в блоке индикации 7, а неиспра вная цепь определяется путем поразрядного сравнения кодов маски и блока индикации.

Несовпадающие разряды блока индикации

7 указывают место цепи, в которой имеется неисправный элемент, так как каждый разряд блока 7 индикации показывает состояние элек1ричсской цепи между двумя контролируемыми точками в данныи момент, и код маски— состояние этой цепи при правильной работе контролируемого устройства.

Проградуировав блок 7 индикации, поставив каждому разряду в соответствие ранг, минимальной для цепи, через которую сигнал проходит в первую очередь, а затем последовательно возрастает, можно локализовать не-!

О исправность. В этом случае фиксируется неисправность той цепи, для которой из несовпавших кода маски и блока 7 индикации ранг минимален. Если таких цепей несколько, то проверке подлежат все.

Предмет изобретения

Устройство для контроля и диагностики неисправностей двоичных схем, содержащее блок

20 матричной памяти, дешифратор строк, соединенный выходами с горизонтальными шинами записи блока памяти, а входом — с входной клеммой устройства, и выходной регистр блока памяти, соединенный, входами с выходами

25 считывания данных блока памяти, о т л и ч аю щеес я тем, что, с целью поиска неизвестных неисправностей и локализации их места, в него введены дополнительно входной регистр, входы которого подключены ко входам

30 устройства, схемы сравнения, причем первый вход первой схемы сравнения соединен со вторым входом второй схемы сравнения, второй — с первым входом третьей схемы, попарно соединенные входы схем сравнения соеди35 иены с выходами входного регистра, выходы схем сравнения соединены с вертикальными шинами записи блока памяти, и блок индикации, вход которого соединен с выходом выходного регистра.

476564

l ! !

I ! ! !

Составитель В. Павленко

Техред М. Семенов

Корректор О. Тюрина

Редактор Л. Утехина

Типография, пр. Сапунова, 2

Заказ 2903/4 Изд. № 930 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4,5