Генератор импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ii 47667 0

Соаэ Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.02.74 (21) 1995527/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.07.75. Бюллетень № 25

Дата опубликования описания 17.11.75 (51) М. Кл. Н 03k Зi53

Н 03k 3/284

Гасударственный комитет

Совета Министров СССР по делам иэобретений и открытий (53) УДК 621.384.6 (088.8) (72) Автор изобретения

В. П. Реута

Казанский ордена Трудового Красного Знамени авиационный институт им. А. Н. Туполева (71) Заявитель

:ъ

I (54) ГЕНЕРАТОР ИМПУЛЪСОВ

Изобретение относится к импульсной технике.

Известен формирователь импульсов, имеющий транзистор, включенный по схеме с общим эмиттером, база которого соединена через резистор с источником положительного напряжения, через последовательно соединенные резистор и конденсатор — с источником отрицательного напряжения, а между базой и источником отрицательного напряжения анодом к базе подключен управляемый диод. Недостатком этого формирователя является наличие двух источников питания.

С целью упрощения схемы генератора импульсов применен транзистор n — р — n-типа, включенный по схеме с общим эмиттером, база которого через первый резистор и последовательно соединенные конденсатор и второй резистор соединена соответственно с отрицательной и положительной шинами источника питания, причем параллельно конденсатору через дополнительный резистор включен тиристор.

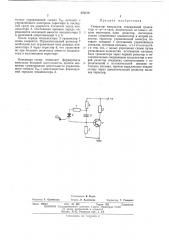

На чертеже показана схема предложенного генератора импульсов.

Транзистор 1 и — р — n-типа с нагрузкой 2 в цепи коллектора подключен к источнику положительного напряжения +Е. База транзистора

1 соединена через конденсатор 3 и резистор

4 г положительной шиной источника питания, а через резистор 5 — с отрицательной шиной того же источника питания. Параллельно конденсатору 3 подключены последовательно соединенные тиристор 6 и резистор 7. Управляющий электрод тиристора 6 соединен с источником управляющих сигналов U„, При включении напряжения питания транзистор 1 сразу же открывается, и на нагрузке 2 выделяется все напряжение питания

10 или часть его за счет того, что в начальный момент конденсатор 3 разряжен, а ток заряда этого конденсатора протекает через резисторы 4, 5, которые образуют делитель напряжения. Напряжение, выделившееся на резисторе

15 5, прикладывается к базе транзистора 1 и открывает его. После заряда конденсатора 3 на базе транзистора 1 потенциал уменьшается до нуля, и транзистор запирается, напряжение на нагрузке 2 становится равным нулю.

20 При поступлении сигнала U на управляющий электрод тиристора 6 последний открывается, через открытый тиристор 6 и огра.ничительный резистор 7 разряжается конденсатор 3, в результате чего транзистор 1 сно25 ва открывается, и на нагрузке 2 выделяется напряжение источника питания.

Если после разряда конденсатора 3 окажется, что управляющий сигнал U> еще присутствует, то конденсатор 3 будет оставаться

30 разряженным, а транзистор 1 открытым. Как

476670

Предмет изобретения

У, Составитель В. Реута

Техред Л. Казачкова

Корректор T. Гревцова

Редактор T. Орловская

Заказ 2694/7 Изд. № 882 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, /К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 только управляющий сигнал U„исчезнет с управляющего электрода тиристора 6, последний сразу же закроется. Начнется заряд конденсатора 3. Постоянная времени заряда определяется величиной емкости конденсатора 3 и величиной сопротивлений 4 и 5.

После заряда конденсатора 3 транзистор 1 снова закроется. Ограничительный резистор 7 необходим для ограничения тока разряда конденсатора 3 через тиристор 6, что существенно при больших величинах емкости конденсатора и маломощном тиристоре.

Описанная схема позволяет формировать импульсы большой длительности, причем возможно суммирование длительности управляющего сигнала У„с длительностью, формируемой зарядом конденсатора 3.

Генератор импульсов, содержащий транзистор n — р — n-типа, включенный по схеме с об5 щим эмиттером, один резистор, последовательно соединенные конденсатор и второй резистор, тиристор, управляющий электрод которого соединен с источником управляющих сигналов, источник питания, о т л и ч а ю щ и й1о с я тем, что, с целью упрощения схемы путем уменьшения количества источников питания, база транзистора через первый резистор и последовательно соединенные конденсатор и второй резистор соединена соответственно с от15 рицательной и положительной шинами источника питания, причем параллельно конденсатору через дополнительный резистор включен тиристор.