Устройство регулирования времени запаздывания в линии задержки

Иллюстрации

Показать всеРеферат

О Л И С А Н И Е <») 476674

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Соцналистечесхнх

Рвспублнн (61) Дополнительное к авт. свил-ву (22) Заявлено 05.11.73 (21) 1971826/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.07.75. Бюллетень № 25

Дата опубликования описания 14.11.75 (51) Ч. Кл. Н 03k 5/13

Государственных комнтвт

Совета Министров СССР яа делам нзооретеннй н OYNpblTHri (53) УДК 621.374.5 (088.8) (72) Авторы изобретения (71) Заявитель

В. М. Полисюк и О. Б. Калганов

Специальное конструкторское бюро по автоматизации прокатного и трубного производства (54) УСТРОЙСТВО РЕГУЛИРОВАНИЯ ВРЕМЕНИ

ЗАПАЗДЫВАНИЯ В ЛИНИИ ЗАДЕРЖКИ

Изобретение относится к устройствам регулирования длительности временного интервала и может быть использовано в системах автоматического управления, содержащих линии задержки импульсного сигнала.

Известно устройство регулирования времени запаздывания в линии задержки, содержащее входной формирователь, выход которого подсоединен к первому входу регулируемой линии задержки, ко второму входу которой через регулирующий орган подсоединен исполнительный элемент. Это устройство не позволяет точно регулировать время запаздывания из-за неидснтичности основной и контрольной линий задержки.

Цель изобретения повышение точности регулирования времени запаздывания в линии задержки.

Поставленная цель достигается благодаря тому, что устройство содержит реверсивный счетчик, формирователь командного импульса, вычитающий счетчик, причем выход входного формирователя соединен со входом суммирования реверсивного счетчика и входом коммутатора непосредственно, а со входом вычитания реверсивного счетчика и счетным входом вычитающего счетчика через линию задержки.

Выход реверсивного счетчика соединен через ключ с входом записи вычитающего счетчика; управляющий вход ключа соединен с выходом коммутатора через одновибратор; выход обнуления вычитающего счетчика соединен с одним входом формирователя командного импульса, другой вход которого подсоединен к выходу формирователя заданного временного интервала, а выход — к исполнительному элементу и входу сброса коммутатора.

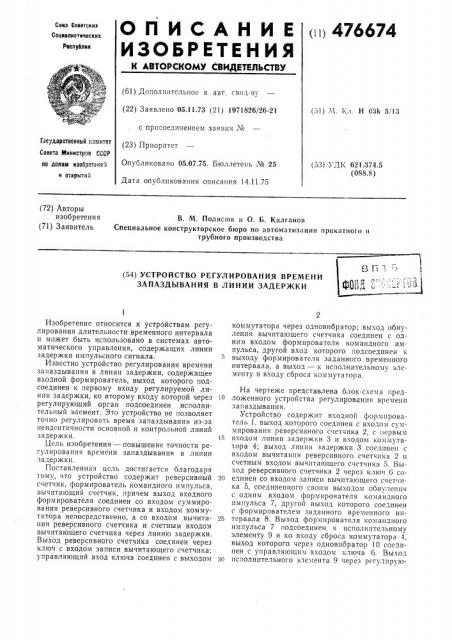

На чертеже представлена блок-схема пред10 ложенного устройства регулирования времени запаздывания.

Устройство содержит входной формирователь I, выход которого соединен с входом суммирования реверсивного счетчика 2, с первым

15 входом линии задержки 3 и входом коммутатора 4; выход линии задержки 3 соединен с входом вычитания реверсивного счетчика 2 и счетным входом вычитающего счетчика 5. Выход реверсивного счетчика 2 через ключ 6 со20 единен со входом записи вычита|ощего счетчика 5, соединенного своим выходом обнуления с одним входом формирователя командного импульса 7, другой выход которого соединен с формирователем заданного временного ин25 тсрвала 8. Выход формирователя командного импульса 7 подсоединен к исполнительному элементу 9 и ко входу сброса коммутатора 4, выход которого через одновпоратор 10 соединен с управляющим входом ключа 6. Выход

30 исполнительного элемента 9 через рсгулпрую476674 щий орган 11 соединен со вторым входом линии задержки 3.

Цикл работы начинается с приходом, например, и-го импульса с выхода формирователя 1.

Этот импульс поступает на вход линии задер>кки 3, запускает коммутатор 4 и записывает единицу в реверсивный счетчик 2, в котором записанное число импульсов равно числу импульсов в линии задержки 3. Сигналом с выхода коммутатора 4 через одновибратор 10 открывается ключ б, и число из реверсивного счетчика 2 переписывается через открытый ключ б в вычитающий счетчик 5.

Таким образом, число в вычитающем счетчике 5 в момент прихода n-ro импульса с выхода формирователя 1 оказывается равным числу импульсов, находящихся в этот момент времени в линии задержки 3.

Импульсы с выхода линии задержки 3 поступают на счетный вход вычитающего счетчика 5, причем каждый импульс вычитает единицу из числа, записанного в счетчике 5. Таким образом, интервал времени, в течение которого производится списывание числа в вычитающем счетчике 5 до нуля, равен времени IIpoхождения и-м импульсом линии задержки 3 и, следовательно, равен действительному времени запаздывания в линии àäåðæêè 3.

Формирователь 7 командного пм:!ульса Ilpoизводит сравнение двух временны. интервалов, измеренного и заданного, и формирование командного импульса длительностью, равной разности временных интервалов.

Командный импульс управляет исполнительным элементом 9, который через регулирующий орган 11 воздействует на линию задержки 3, устанавливая время запаздывания равным заданному. Задним фронтом командного импульса с выхода формирователя 7 коммутатор 4 возвращается в исходное состояние. H I этом заканчивастся цикл измерения и регулирования.

Первым же импульсом с формирователя 1, пришедшим после окончания предыдущего цикла, коммутатор 4 запускается вновь, и начинается новый цикл работы устройства.

Таким образом, данное устройство является замкнутым непосредственно по регулируемому, араметру, причем измеренное в каждом цикле работы время запаздывания строго равно времени прохождения рабочих импульсов че-!!! рез основную линию задержки, что обеспечигает более высокую точность регулирования, чем в известном устройстве.

Предмет изобретения !

Устройство регулирования времени запаздывания в линии задержки, содержащее входной формирователь, выход которого;юдсоединен к первому входу регулируемой линии

2О задержки, «о второму входу которой через регулирующий орган подсоединен исполнительный элемент, отл и ч а ю ще ес я тем, что, с целью повышения точности регулирования, устройство содержит реверсивный счетчик, "3 формирователь командного импульса, вычитающий счетчик, причем выход входного формирователя соединен со входом суммирования реверсивного счетчика и со входом коммутатора непосредственно, а со входом вычитания зо реверсивного счетч !ка и со счетным входо вычптающего счетчика через лини!о задержки, а выход реверсивного счетчика соеди!!ен !ерез ключ с входом за!!иси вычптающего счетчика, ; ри этом управля!ощий вход ключа соединен зз с вы Уо."Iîì коммутатора через одновпбратор, а выход обнуления вычитающего счетчика с<>едппсн с одним входом формирователя командного импульса, друго!! вход которого подсоединен к выходу формирователя заданного и! временного интервала, а выход — к исполнитсгп пох!у элементу и ко входу сброса коммутатора.

476674

Составитель Л. Федорова

Техред Л. Казачкова

Корректор В Брыксина

Редактор T. Орловская

Типография, пр. Сапунова, 2

Заказ 2744!13 Изд. Мо 884 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5