Реверсивный счетчик

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (»1 476687 ааааа Ооввтеких

Социалистических

Реваубаик,(61) Зависимое от авт. свидетельства (22) Заявлено 20,07.73 (21) 1946549/26-21 с присоединением заявки № (32) Приоритет

Опубликовано 05.07.75. Бюллетень ¹ 25

Дата опубликования описания 17.11.75 (51) Ч. Кл. H 03k 23, 00

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.374.32 (088.8) (72) Авторы изобретения

В. А. Грехнев и В. T. Тряпицын (71) Заявитель (54) РЕВЕРСИВНЫЙ СЧЕТЧИК

Изобретение относится к вычислительной технике и предназначено для суммирования или вычитания последовательности входных им пульсов.

Известен реверсивный счетчик на элементах И вЂ” HE, каждый разряд которого выполнен на триггере памяти, двух коммутационных триггерах и двух схемах И вЂ” HE, причем единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход первого коммутационного триггера соединен с нулевым входом второго коммутационного триггера и со входом первой схемы И вЂ” HE. Нулевой выход второго коммутационного триггера соединен со входом второй схемы И вЂ” HE, а единичный выход второго коммутационного триггера соединен с нулевыми входами триггера памяти и первого коммутационного триггера и со входом первой схемы И вЂ” HE. Шина разрешения сложения соединена со входом первой схемы И вЂ” HE, шина разрешения вычитания соединена со входом второй схемы И вЂ” HE, а шина импульса счета соединена с нулевым входом первого коммутационного триггера и с единичным входом второго коммутационного триггера. Выход первой схемы И вЂ” HE соединен с нулевым входом первого коммутационного триггера следующег о разряда, выход второй схемы И вЂ” 11Е соединен с нулевым входом первого н с едшзнчным входом второго коммутационных триггеров следую5 щего разряда.

Недостатком известного реверсивного счетчика является большое число межразрядных связей и сложность.

Цель изобретения — унро пенне устройства.

10 Поставленная цель достигается тем, что выход первой схемы И вЂ” Hl соединен с единичным входом первого коммутационного триггера следующего разряда, выход второй схемы И вЂ” НЕ соединен с нулевым входом

15 второго коммутационного триггера следующего разряда.

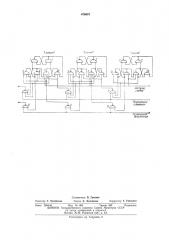

На чертеже показана схема предложенного реверсивного счетчика.

Схемы И вЂ” HE 1 и 2 образуют триггер

20 памяти, схемы И вЂ” HE 3» 4 — второй коммутационный триггер, а схемы И вЂ” HE 5 и

6 — первый коммутацнонньш триггер, схемы

И вЂ” HE 7 н 8 выполняют свойственные им логические функции.

"5 В режиме суммирования на входы схем

И вЂ” НЕ 7 подаются сигналы, равные логической единице, а на входы схем И вЂ” НЕ 8— сигналы, равные логическому нулю. Первый разряд счетчика работает как обычный триг30 гер со счетным входом. Поскольку на выходах

476687

15 схем И вЂ” НЕ 8 сигнал равен логической единице, то срабатывание 2-го разряда осуществляется лишь при наличии сигнала переноса с выхода схемы И вЂ” НЕ 7 первого разряда, что указывает на то, что триггер памяти первого разряда находится в единичном состоянии.

Если сигнал переноса отсутствует, т. е. равен логическому нулю, то на выходе схемы И—

HE 6 второго разряда появляется логическая единица, независимо от того, в каком состоянии находится триггер памяти второго разряда. Поскольку импульс счета отсутствует, то на выходах схем И вЂ” HE 4 и 5 также будут логические единицы, а следовательно, на выходе схемы И вЂ” НЕ 7 второго разряда появится логический нуль, т. е. сигнал переноса и в третий разряд отсутствует, хотя триггер памяти второго разряда может находиться в это время в состоянии «единица». Логический нуль будет и на выходе схемы И вЂ” НЕ 3 второго разряда, поэтому с приходом импульса счета схема И вЂ” HE 4 не сработает, не сработает и схема И вЂ” НЕ 5 из-за отсутствия сигнала переноса.

При наличии сигнала переноса каждый разряд счетчика работает как счетный триггер.

Наличие или отсутствие сигнала переноса на выходе схемы И вЂ” НЕ 7 запоминается па время действия тактирующего импульса, что исключает повторное срабатывание триггеров в течение одного и того же импульса счета.

Сигнал переноса на выходе схемы И вЂ” HE 7 данного разряда равен сумме сигналов переноса из предыдущих младших разрядов и сигнала состояния триггера памяти данного разряда. Процесс суммирования выполняют схемы И вЂ” НЕ 6 и 7. Срабатывание третьего разряда происходит лишь при наличии сигнала переноса на схеме И вЂ” HE 7 второго разряда, что указывает на то, что во втором разряде записана единица и имеется сигнал переноса на выходе схемы И вЂ” НЕ 7 первого разряда, т. е. что и в первом разряде записана единица. Таким образом, с приходом пм пульса счета триггеры во всех трех разрядах изменят свое состояние. Срабатывание и-го разряда осуществляется лишь при наличии сигнала переноса с выхода схемы И вЂ” HE 7 (n — 1)-го разряда счетчика, что указывает на то, что в 1, 2, ..., (n — 1) разряде находятся единицы.

В режиме вычитания срабатывание и-ro разряда осуществляется лишь при наличии

95 ,.-0

30 сигнала заема с выхода схемы И вЂ” НЕ 8 (n — 1) -ro разряда счетчика, что указывает на то, что в 1, 2, ..., (п — 1) разрядах триггеры памяти находятся в состоянии «нуль».

Наличие или отсутствие сигнала заема на выходах схем И вЂ” HE 8 запоминается на время действия тактирующего импульса, что исключает повторное срабатывание триггеров в течение одного и того же импульса счета. Таким образом, работа схемы в режиме вычитания аналогична работе схемы в режиме суммирования.

Предмет изобретения

Реверсивный счетчик на элементах И вЂ” НЕ, каждый разряд которого выполнен на триггере памяти, двух коммутационных триггерах и двух схемах II — HE, причем единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход первого коммутационного триггера — с нулевым входом второго коммутационного триггера и со входом первой схемы И вЂ” НЕ, нулевой выход второго коммутационного триггера соединен со входом второй схемы И—

НЕ, а единичный выход второго коммутационного триггера соединен с нулевыми входами триггера памяти и первого коммутационного триггера и со входом первой схемы И вЂ” НЕ, шина разрешения сложения соединена со входом первой схемы И вЂ” НЕ, шина разрешения вычитания соединена со входом второй схемы И вЂ” HE, а шина импульса счета соединена с нулевым входом первого коммутационного триггера и с единичным входом второго коммутационного триггера, выход первой схемы И вЂ” HE соединен с нулевым входом первого коммутационного триггера последующего разряда, выход второй схемы И вЂ” НЕ соединен с нулевым входом первого и с единичным входом второго коммутационных триггеров последующего разряда, о т л и ч а ющи йся тем, что, с целью упрощения устройства, выход первой схемы И вЂ” НЕ соединен с единичным входом первого коммутационного триггера последующего разряда, а выход второй схемы И вЂ” НЕ соединен с нулевым входом второго коммутационного триггера последующего разряда.

476687

2 v-.çãÿ

3 РазРЯР

JO3, ÷ Ó вЂ” -т1 (Умпульс

Сапорта

1

Разрешение сльке и

4 Рф 7РШРФРР

®аул АР/

Составитель В. Грехнев

Техред Л. Казачкова

Корректор T. Гревцова

Редактор Т. Орловская

Типография, пр. Сапунова, 2

Заказ 2694/16 Изд. № 882 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5