Устройство цифровой когерентной фильтрации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (61) Дополщггельное к явт. свнд-ву (22) Заявлено 08.06.72 (21) 1794001/26-9 с присоединением заявки № (51) И. Кл. И 04Ь 1,/10

Совета Министров СССР по делам изобретений н открытий

Опубликовано 05.07.75. 1>юлл Tc. Irr) IY > 25

Дата опубликования описания 11.11.75 (53) УДК 621.372.57 (088.8) (72) Авторы изобретения

В. А. Лихарев, Г. Н. Валаев, В. Л. Буйлов и О. Н. Линников

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (71) Заявитель (54) УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТИОЙ

ФИЛЬТРАЦИИ

Государственный комитет (23) Приоритет

Изобретение относится к радиолокации, в частности к области когерентного приема.

Известно устройство цифровой когерентной фильтрации, содержащее аналого-цифровой преобразователь, два накапливающих сумматора, генератор тактовых импульсов, схему

«ИЛИ».

Предлагаемое устройство отличается тем, что, с целью повышения его надежности, c»г нальный Bbrxo;I, аналого-цифрового преобразователя соединен со счетными входами накапливающих сумматоров, а знаковый — с управляющими входами накапливающих сумматоров через соответствующую схему сложения по модулю 2; генератор тактовых импульсов соединен с одной схемой сложения по модулю 2, а со второй — через элемент задержки.

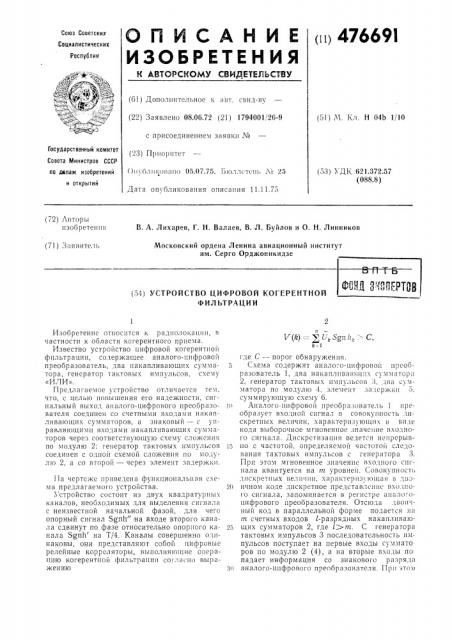

11а чертеже приведена функциональная схема предлагаемого устройства, Устройство состоит из двух квадратурных каналов, необходимых для выделения сигналя с неизвестной начальной фазой, для чего опорный сигнал Sgnh" на входе второго канала сдвинут по фазе относительно опорного канала Sgnh на Т/4, Каналы совершенно одинаковы, они представляют собой цифровые релейные корреляторы, выполняющие операцию когерентной фильтрации согласно выражению где С вЂ” порог обнаружения.

5 Схема содержит анало;о-цифровой преобразователь 1, два накапливаю цпх сумматора

2, генератор тактовых импульсов 3, два сумматора по модулю 4, элемент задержки 5, суммирующую схему 6.

1о Аналого-цифровой преобразователь 1 преобразует входной сигнал в совокупность дискретных величин, характерпзующпx в виде кода выборочное мгновенное значение входного сигнала. Дискретизация ведется непрерывно с частотой, определяемой частотой следования тактовых импульсов с генератора 3.

Прн этом мгновенное значение входного сигнала квантуется íà rn уровней. (овокупност1 дискретных величин, характеризующая в дво20 ичном коде дискретное представление входного сигнала, запоминается в регистре яняло. .оцифрового преобразователя. Отсюда 1;Iвои 1ный код в параллельной форме подается ня

m счетных входов 1-разрядных накапливаю25 щих сумматоров 2, где г)пг. С генератора тактовых импульсов 3 последовательность импульсов поступает на первые входы суммато ров по модулю 2 (4), а на вторые входы по падает информация со знакового разряда

3rl аналого-цифрового преобразователя Прп этом

47669!

15

Составитель Е, Ковалева

Тскре:(Л. Ка <апкова

Корректор Л. Дсиискииа

Реда:тор Б. Феда) ов

Заказ 2743/15 Изд. № 905 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 сумматор по модулю 2 (-)) 8(<)j)01<) !сиiiiii.< последовательность импульсов с i сцерато;а тактовых импульсов:3 приходит сд)цшутоц элементом задержки 6 ца Т|А. Таких! ооразом формируются опорные сигналы Sgnh ii

Sgnh". Выходы сумматоров цо мо,(ули> 2 «oñдинены с управляющими входамц цакацлцвающих сумматоров 2, которые в зависимост;1 от знака опорных сигналов Sgnh и Sgnh" складывают или вычитают поступак)щце с аналого-цифрового преобразователя 1 вхо !цыс сигна Ibi. Кроме того, в сумматоры 2 записывается 8 Обратном,,воцчцом ко,(« iloj)()i обнаружения С. Онц ilo,ic(ит(.!8(!!от входцы( сигналы, поступающие на нцх за и iie!)1!одо!1, и при превышении nop01 с ш!дакгг 1<3 I)xo,<( суммирующей схемы 6 си!.ца обцаружецц».

B противном случае на вход схемы 6 прцхо-!!èò нуль. По прошествии и перно 108 суммаl ! " оону » <)гся, ц < ð<)n«<с <)<»I;Ij>)-;кенця и "ilil,3«тc". за !080.

I I j> C,(I C .1» 3 u () j) e e II »»

«. 1 )<) !!«тl 0 цц(!));)()80!! 1(()! (р(ц! цой фц. !1 т)) ll с ).(«;) i(3::,:(,. 3113!;)10-i Iiôj)08OI! цр«обрц,лватс,li,, —,83 пака:!лцваю<ццх сумматора,: «цсратор I ;)I ) о;- ых цм !ульсов, схему «И.")И»

0 Tл цч а ющеес я тем, что, с целью повышения его надежности, сигнальный выход аналогn-цифрового п )еобразователя сое!i!ir«li

CO C !(. TЦЫМЦ ВХОД3МЦ ЦанаПЛЦ83)ОIЦИХ C> Ì)I3T0Ð()В, 3 Зii 3 КО ВЫ и — — С чПР38ЛЯ101ЦIDI ii БХОД3мц накапливающих сумматор(ц! через соотв тству!0(цую схему слож ill!H цо модулк> 2, црц э гом г«II(.))(IToj) .ò;lêòo«ûê импульсов сосдццсц с одной схемой сложения по модулю 2 непосредственно, а со второй — через элемент задержки.