Стабилизатор переменного напряжения

Иллюстрации

Показать всеРеферат

0 П И С А Н Й Е

ИЗОБРЕТЕНИЯ

00 477403

Сева Оовотскйм т,оциалистичесииа

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08.01.73 (21) 1869200/24-7 с присоединением заявки № (23) Приоритет

Опубликовано 15.07.75. Бюллетень № 26 (51) М. Кл. б 05f 1/44

Государственный комитет

Совета Министров СССР по делам изобретений (53) УДК 621.316.722,1 (088.8) и открытий

Дата опубликования описания 10.10.75 (72) Авторы изобретения

И. С. Колтыпин, А. М. Прядкин, В. М. Титкин, М. Я. Танаев и Л. М. Баконин (71) Заявитель (54) СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

Изооретение относится к области электротехники и может быть использовано в качестве стабилизированного источника для питания устройств автоматики и вычислительной техники, Известны стабилизаторы переменного напряжения, содержащие трехфазный силовой трансформатор, управляемый тиристорный трехфазный выпрямитель, сглаживающий фильтр, измерительный и пороговый узлы, источник опорного напряжения, формирователь синхроимпульсов, орган формирования HMпульсов включения тиристоров в момент прохождения переменного напряжения через нуль, триггеры основного и дополнительного регистров и блок логики. Недостатком таких стабилизаторов является неравномерное распределение нагрузки между фазами питающего напряжения, что приводит к снижению надежности из-за перегрузки и выхода из строя отдельных тиристоров или ке вызывает завышение номинальной мощности тиристоров, что, в свою очередь, влечет за собой увеличение габаритов стабилизатора и его стоимости.

Для равномерного распределения нагрузки между фазами питающего напряжения, повышения надежности, уменьшения габаритов и снижения стоимости в предлагаемом стабилизаторе па одни входы блока логики подключен выход порогового узла, а па другие — еднничные выходы триггеров дополнительного регистра, на первые установочные в «I» и «О» входы которых подключены одни из выходов формирователя синхроимпульсов, причем вто5 рые установочные в «1» и «О» логические входы триггеров дополнительного регистра подключены к соответствующим нулевым выходам триггеров основного регистра, единичными выходами подсоединенных к соответствую1Q щим входам органа формирования импульсов включения тиристоров, Первые установочные в «1» и «О» входы триггеров основного регистра подключены к выходу блока логики, а вторые установочные в «1» и «О» входы — к дру15 гим выходам формирователя сннхроимпульсов.

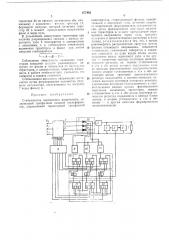

На чертеже дана блок-схема описываемого стабилизатора.

Стабилизатор состоит из трехфазного сило20 вого трансформатора 1, управляемого тиристорного трехфазного выпрямителя 2, сглаживающего фильтра 3, измерительного 4 и порогового 5 узлов, источника 6 опорного напряжения, нагрузки 7, формирователя 8

25 синхроимпульсов, органов 9 — 11 формирования импульсов включения тирнсторов, основного 12 и дополнительного 13 регистров управления и блока 14 логики. Основной регистр управления выполнен на триггерах 15 — 17, ЗО блок логики — на логических элементах «И»

477403

15

18 — 20, а дополнительный регистр — на триггерах 21 — 23. Трехфазный выпрямитель 2 состоит из тиристоров 24 — 26.

Стабилизатор работает следующим обра,oì.

На вход трехфазного силового трансформатора 1 подаются три фазы Аь В и С> переменного напряжения. Со вторичных обмоток трансформатора снимается напряжение фаз

А, В и С для получения стабилизированного напряжения и напряжение (фазы а, в, с, аь в и ci) для формирования синхроимпульсов.

Вторичное переменное напряжение фаз А — С подается а управляемый выпрямитель 2, где оно выпрямляется, затем сглаживается фильтром 3, стабилизируется и в виде постоянного напряжения поступает а нагрузку 7.

Постоянное сглаженное напряжение через измерительный узел 4 поступает па первый вход порогового узла 5, на второй вход которого подается опорное напряжение, снимаемое с выхода источника 6. Сигнал с выхода порогового узла 5 поступает на первые входы логических элементов «И» 18 — 20 блока 14 логики, на вторые входы которых подключены соответствующие единичные выходы триггеров

21 — 23 дополнительного регистра 13.

Формирователь 8 синхроимпульсов вырабатывает серию сдвинутых по времени импульсов, синхронизированных с папря кением питающей сети. На логические установочные входы триггеров дополнительного регистра 13 подаются синхроимпульсы, снимаемые с формирователя 8, и сигналы обратной связи, снимаемые с нулевых выходов триггеров 15 — 17 основного регистра 12.

Выходы логических элементов «И» блока 14 логики подключены к первым логическим входам установки в «О» триггеров 15 — 17 основного регистра 12, на вторые логические входы установки в «О» и на логические входы установки в «1» которых в момент прохождения вторичного силового напряжения через нуль подаются синхроимпульсы с формирователя 8.

Нулевые выходы триггеров основного регистра 12 подключены обратной связью к соответствующим входам триггеров дополнительного р ег истр а 13.

В исходном состоянии стабилизатора триггеры основного регистра устанавливаются так, что их состояние обеспечивает поддержание номинального значения напряжения на нагрузке.

Если напряжение на нагрузке меньше номинального, то пороговый узел 5 вырабатывает сигнал в виде логической «1», абсолютное значение которого определяется выбранной системой логических элементов. Этот сигнал подается на логические элементы «И»

18 — 20. Предположим, что перед этим моментом времени триггер 15 основного регистра 12 находится в нулевом состоянии, т. е. на нулевом выходе триггера 15 имеется сигнал логической «1». Орган 9 формирования импульсов включения тиристора 24 по сигналу логичес25

ЗО

65 кого «О», снимаемому с единичного выхода триггера 15, формирует импульс, который включает тиристор 24 в момент прохождения напряжения фазы А через нуль.

По совпадении сигнала логической «1», снимаемого с пулевого выхода триггера 15, и cGответствующего синхроимпульса триггер 21 дополнительного регистра 13 переключается в нулевое состояние, а триггер 22 — в единичное. Переключение триггера 21 в íулевое состояние запрещает прохождение сигнала с порогового узла 5 через логический элемент «И»

18 на переключение триггера 15 основного регистра 12. Переключение триггера 22 в единичное состояние разрешает прохождение сигнала с порогового узла через логический элемент «И» 19 на логический вход триггера 16 основного регистра 12 и при получении соответствующих синхроимпульсов устанавливает триггер 16 в нулевое состояние.

Триггер 15 соответствующим синхроимпульсом устанавливается в единичное состояние

Орган 10 формирования импульсов включения тиристора 25 по сигналу логического «О», снимаемому с единичного выхода триггера 16, формирует импульс, который включает тиристор 25 в момент прохождения напряжения фазы В через нуль.

По совладении сигнала логичсской «1 >, снимаемого с пулевого выхода триггера 16, и синхроимпульса триггер 22 дополнительного регистра 13 переключается в нулевое состояние, а триггер 23 — в единичное. Переключе ние триггера 22 в нулевое состояние запрещает прохождение сигнала с порогового узла 5 через логический элемент «И» 19 на переключение триггера 16 основного регистра 12. Переключение триггера 23 в единичное состояние позволяет установить триггер 17 основного регистра 12 в нулевое состояние при наличии синхроимпульса. Синхроимпульсом триггер 16 устанавливается в единичное состояние. Орган

11 формирования импульсов включения тиристора 26 по сигналу логического «О», снимаемому с единичного выхода триггера 17, формирует импульс, который включает тпристор 26 в момент прохождения напряжения фазы С через нуль.

По совпадении сигнала логической «1», снимаемого с нулевого выхода триггера 17, и синхроим пульса триггер 21 дополнительного регистра 13 переключается в единичное состояние, а триггер 23 — в нулевое. Переключение триггера 21 в единичное состояние разрешает прохождение сигнала с порогового узла 5 через логический элемент «И» 18 на переключение триггера 15 в нулевое состояние при наличии синхроимпульса. Синхроимпульсом триггер 17 устанавливается в единичное состояние. Переключение триггера 23 в нулевое состояние запрещает прохождение сигнала с порогового узла 5 через логический элемент «И» 20 на переключение триггера 17.

Орган 9 формирования импульсов включении

477403

Б7 тиристора 24 по сигналу логического «0», снимаемому с единичного выхоча триггера 15, формирует импульс, который вклlочает тиристор 24 в момент прохождения напряжения фазы А через нуль.

В дальнейшем коммутация тиристоров при наличии разрешающего сигнала с выхода порогового узла 5 повторяется в соответствии с описанным, т. е. соблюдается очередность включения тиристоров в фазах при ля!бой нагрузке стабилизатора — -А- В-- С вЂ”. !

Соблюдение очередности включения тиристоров позволяет создать равномерную нагрузку по фазам и избаннп,ся от пе;:егрузки тиристоров, а следогательно, повысить надежность в работе стабилизатора, умсньни!т1, его габариты и снизить стоимость.

Стабилизация выходного напряжения достигается путем регулирования количества полуволн напряжения, поступающего на нагрузку

7 через фильтр 3.

Предмет изобретения

Стабилизатор переменного напряжения, содержащий трехфазный силовой трансформатор, управляемый тиристорный трехфазный выпрямитель, сгла>кива!О!ци! фильтр, нзмерительнь!й и пороговый узлы, источник опорного напряжения, формирователь синхроимпульсоВ Орган формировани!! и мн льсо Г Вкл1очения тивисторов в моме1гг прохождения переменного напряжения через нуль. триггеры основного и дополнительного регистров и блок логики, отл ич а ю щи и с я тем, что, с целью равномерного распределения нагрузки между

10 фазами питающего напряжения, повышения !!Вде>кностн, уменьшения габаритов и снижеItI.>I стоимости, IIQ Одни Входы блока логики

i,î II ëIo÷åII выход порогового узла, а на другие — сдини шые выходы триггеров допол1Ш15 тельного регистра, на первые установочные в «1» и «0» входы когорь;х подкл!О1!ен! Одни из выходов формирователя сиi.хроимпульсов, !!ричем вторые установочные г, «1» и «0» логические входы триггеров дополнительного

20 регистра подключены к соответствующим нулевым выходам триггеров основного регистра, единичными выходами подсоединенных к соответствующим входам органа форх!Ирован11я импульсов включения тиристоров, первые

25 установочные в «1» и «0» входы триггеров основного регистра подключены к выходу блока логики, а вторые установочные в «1» и «0» входы — к другим выходам формирователя синхроимпчльсов.