Комбинационный сумматор-вычитатель

Иллюстрации

Показать всеРеферат

ч л

ОП ИС NE

ИЗОБРЕТЕНИЯ йц 477410

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 17.07.72 (21) 1814243/18-24 с,присоединением заявки № (23) Приоритет

Опубликовано 15.07.75. Бюллетень ¹ 26

Дата опубликования описания 09.12.75 (51) М. Кл. б 06f 7/385

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.325.5 (088.8) (72) Автор изобретения

В. Н. Газиян (71) Заявитель (54) КОМБИНАЦИОННЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ

Изобретение может быть использовано в дискретных устройствах автоматики и вычислительной техники.

Известна схема комбинационного сумматора-вычитателя, содержащая два формальных нейрона с порогами +1 и +2 и элементы

ИЛИ.

Недостатком известной схемы является большое количество оборудования.

Цель изобретения заключается в уменьшении количества оборудования.

Эта цель достигается тем, что в предлагаемом сумматоре-вычитателя первые выходы обоих нейронов, имеющие вес «+1», объединены и подключены к шине переноса из предыдущего разряда, вторые входы обоих нейронов, имеющие вес «+1», объединены и подключены к шине перьвого слагаемого (вычитаемого), третьи входы обоих нейронов, имеющие вес «+1», и первые входы обоих элементов «ИЛИ» объединены и подключены к шине второго слагаемого (уменьшаемого), четвертые входы обоих нейронов, имеющие вес «+1», и вторые входы обоих элементов

«ИЛИ» объединены и подключены к управляющей шине, выходы первого и второго элементов «ИЛИ» соединены со входами, имеющими sec « — 2», соответственно первого и второго формального нейрона, а инверсный выход первого формального нейрона соединен со входом второго формального нейрона, имеющим вес «+2».

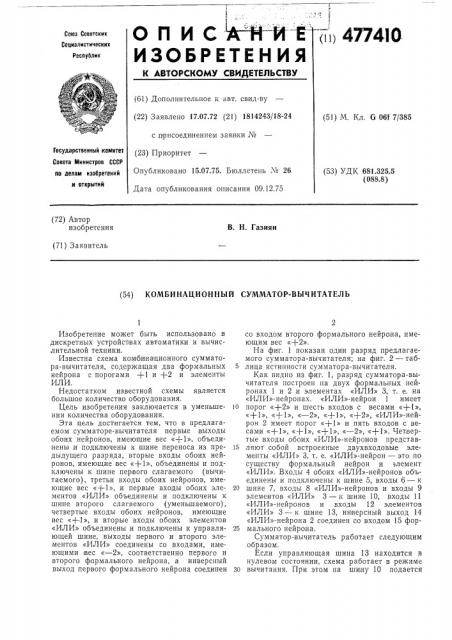

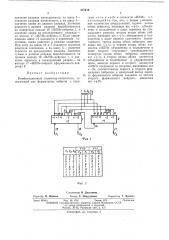

На фиг. 1 показан один разряд предлагаемого сумматора-вычитателя; на фиг. 2 — таб5 лица истинности сумматора-вычитателя.

Как видно из фиг. 1, разряд сумматора-вычитателя построен на двух формальных нейронах 1 и 2 и элементах «ИЛИ» 3, т. е. на

«ИЛИ»-нейронах. «ИЛИ»-нейрон 1 имеет

10 порог «+2» и шесть входов с весами «+1», «+1», «+1», « — 2», «+1», «+2», «ИЛИ»-нейрон 2 имеет порог «+1» и пять входов с весами «+1», «+1», «+1», « — 2», «+1». Четвертые входы обоих «ИЛИ»-нейронов представ15 ляют собой встроенные двухвходовые элементы «ИЛИ» 3, т. е. «ИЛИ»-нейрон — это по существу формальный нейрон и элемент

«ИЛИ». Входы 4 обоих «ИЛИ»-нейронов объединены и подключены к шине 5, входы 6 — к

20 шине 7, входы 8 «ИЛИ»-нейронов и входы 9 элементов «ИЛИ» 3 — к шине 10, входы 11

«ИЛИ»-нейронов и входы 12 элементов

«ИЛИ» 3 — к шине 13, инверсный выход 14

«ИЛИ»-нейрона 2 соединен со входом 15 фор25 мального нейрона.

Сумматор-вычитатель работает следующим образом.

Если управляющая шина 13 находится в нулевом состоянии, схема работает в режиме з0 вычитания. При этом на шину 10 подается

477410

Предмет изобретения

У Я1К2К

Фиг. /

Фиг. 2

Составитель И. Долгушева

Техред E. Подурушина

Редактор И. Шубина

Корректор Т. Фисенко

Заказ 2934/1 Изд. № 1742 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )Ê-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 значение разряда уменьшаемого, на шину 7— значение разряда вычитаемого, а на шину 5— значение заема из данного разряда. Значение разности в данном разряде вырабатывается на инверсном выходе 16 «ИЛИ»-нейрона 1, а значение заема из последующего разряда— на выходе 17 «ИЛИ»-нейрона 2. Если управляющая шина 13 находится в единичном состоянии, схема работает в режиме сложения.

При этом на шины 10 и 7 подаются значения разрядов слагаемых, а на шину 5 — значение переноса из предыдущего разряда. Значение суммы,в данном разряде вырабатывается на прямом выходе 18 «ИЛИ»-нейрона 1, а значение переноса в последующий разряд — на выходе 17 «ИЛИ»-нейрона (формального нейрона) 2.

Комбинационный сумматор-вычитатель, содержащий два формальных нейрона с порогами «+1» и «+2» и элементы «ИЛИ», отл и ч а ю шийся тем, что, с целью уменьшения количества оборудования, первые входы обоих нейронов, имеющие вес «+1», объединены и подключены к шине переноса из предыдущего разряда, вторые входы обоих нейронов, имеющие вес «+1», объединены и подключены к шине первого слагаемого (вычитаемого), третьи входы обоих нейронов, име1о ющие вес «+1», и первые входы обоих элементов «ИЛИ» объединены и подключены к шине второго слагаемого (уменьшаемого) четвертые входы обоих нейронов, имеющие вес «+1», и вторые входы обоих элементов

15 объединены и подключены к управляющей шине, выходы первого и второго элементов

«ИЛИ» соединены со входами, имеющими,вес

« — 2», соответственно первого и второго формальных нейронов, а инверсный выход перво20 го формального нейрона соединен со входом второго формального нейрона, имеющим вес «+2».