Диагностическое вычислительное устройство

Иллюстрации

Показать всеРеферат

° —,, л

МлГ..л«,;:««- °:;л «ОП ИСАН ИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистимеских

Республик » 477421 (61) Зависимое от авт. свидетельства— (22) Заявлено 05.07.73 (21) 1941273/18-24 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 15.07.75. Бюллетень № 26

Дата опубликования описания 09.03.76 (51) Ч. Кл. G06f 15/42

1осударстввнный комитет

Совета Министров СССР по девам изобретений и открытий (53) УДК 681 322 (088.8) (72) Авторы изобретения С. Н. Басович, А. Д. Семенов, И. К. Хрусталев и К. Н. Чернецов

Пензенский политехнический институт (71) Заявитель (54) ДИАГНОСТИЧЕСКОЕ ВЫЧИСЛИТЕЛЬНОЕ

УСТРОЙСТВО

Изобретение относится к области автоматики и вычислительной техники, Известно диагностическое вычислительное устройство, содержащее вращающийся барабан, диск со спиральными канавками для хранения постоянной информации, диск для хранения оперативной информации, датчики кодовых меток постоянной и оперативной информации, решающий блок.

Недостатком известного устройства является снижение надежности его работы при повышении плотности записи постоянной информации. Снижение надежности объясняется тем, что при высокой плотности записи постоянной информации возникают сбои за счет неточности ориентации дисков относительно друг друга и за счет неточности нанесения кодовых меток оперативной информации.

Цель данного изобретения заключается в повышении надежности работы устройства без повышения требований к точности ориентации дисков относительно друг друга и к точности нанесения кодовых меток оперативной информации.

Сущность изобретения заключается в том, что в устройство введены блок Bblp200Têè синхросигнала, распределители, счетный вход первого из которых подключен к выходу бло2 ка тактовых меток и ко входу первого блока декодирования, выход которого подключен к управляющему входу первого распределителя; первая группа схем «И», первые входы

5 которых подключены к соопветствующим выходам первого распределителя, а вторые входы объединены и подключены к выходу блока кодовых меток оперативной информации, триггеры, первые входы которых подключены

1о к выходам соответствующих схем «И» первой группы; вторая группа схем «И», первые входы которых подключены к единичным выходам соответствующих триггеров, второй вход р-й схемы «И» второй группы, кроме

15 первой схемы «И», подключен ко второму входу (р-1)-го триггера и к р-му выходу второго распределителя; второй вход первой схемы «И» второй группы подключен ко второму входу последнего триггера и к первому

20 выходу второго распределителя, выходы схем «И» второй группы соединены соответственно со входами схемы «ИЛИ», выход которой соединен с первым входом решающего блока, ко второму входу которого подключен выход блока кодовых меток постоянной информации и вход блока выработки синхросигнала, выход которого соединен со счетным входом второго распределителя, управляющий вход которого подключен к выходу

3о второго блока декодирования, вход которого

477421

3 соединен с выходом блока кодовых меток постоянной информации.

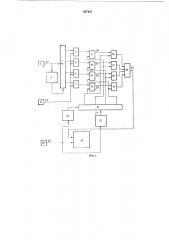

На фиг. 1 изображена схема устройства; на фиг. 2 — временные диграммы.

Блок 1 тактовых меток, нанесенных, например, на поверхности барабана, подключен к счетному входу первого распределителя 2 и к входу первого блока декодирования 3, выход которого подключен к управляющему входу первого распределителя. Выходы первого распределителя 2 соединены с первыми входами схем «И» 4, 5, 6, 7, образующих первую группу схем «И».

Вторые входы схем «И» 5 — 7 объединены и подключены к блоку 8 кодовых меток оперативной информации. Выходы схем «И» 4 — 7 подключены к первым входам триггеров

9 — 12. Вторые входы триггеров соединены с выходами второго распределителя 13 и со вторыми входами схем «И» 14 — 17, образующих вторую группу схем «И». При этом второй вход р-й схемы «И» второй группы подключен ко второму входу (р — 1) -го триггера и к р-му выходу второго распределителя, а второй вход первой схемы «И» 14 второй группы подключен ко второму входу последнего триггера 12.

Количество схем «И» в каждой группе и количество триггеров на фиг. 1 равно четырем, Практически это количество зависит от предельной погрешности ориентации дисков относительно друг друга, предельной погрешности нанесения кодовых меток оперативной внформации и .может быть больше четырех.

Выходы схем «И» 14, 15, 16, 17 подключены ко входам схемы «ИЛИ» 18, выход которой соединен с первым входом решающего блока 19. Ко второму входу решающего блока подключен блок 20 кодовых меток постоянной информации и вход блока 21 выработки синхросигнала.

Выход этого блока подключен к счетному входу второго распределителя 13. Управляющий вход второго распределителя подключен к выходу второго блока декодирования 22, вход которого соединен с выходом блока 20 кодовых меток постоянной информации.

На фиг. 2 представлены сигналы, формируемые на соответствующих выходах узлов, входящих в схему фиг. 1: тактовый сигнал с выхода блока 1 тактовых меток — 23; сигнал с выхода блока 8 кодовых меток оперативной информации — 24; сигнал с выхода блока 20 кодовых метснк постоянной информации — 25; сигнал с единичного выхода триггера 9 — 26; сигнал с единичного выхода триггера 10 — 27; сигнал с единичного выхода триггера 11 — 28; сигнал с единичного выхода триггера 12 — 29; сигнал с выхода схемы «ИЛИ» 18 — 30; сигнал с выхода блока 21 выработки синхросигнала — 31;

Устройство работает следующим образом.

В исходном состоянии с блока 1 тактовых меток поступают сигналы 23, с блока 20 кодовых меток постоянной информации посту65

24 — устанавливается триггер 11 в единичное состояние;

4 пают отдельыые кодовые последовательности 25, не несущие информации о вероятностях признаков. Блок 21 выработки синхросигнала выделяет из кодовой последователь6 ности синхросигналы 31, совпадающие по времени с концом прошедшей кодовой последовательности. Сигнал с выхода блока 8 отсутствует.

С|инхросигналы 31 поступают на счетный

10 вход распределителя 13 и продвигают сигнал «1» на его выходах. В результате этого триггеры 9, 10, 11, 12 устанавливаются в нулевое состояние.

Перед приходом кодовых сигналов 24, не16 сущих информацию о наличии тех или иных признаков, блок декодирования 3 вырабатывает импульс и устанавливает сигнал «1» на первом (верхнем по ориг. 1) выходе распределителя 2.

20 Приходящий в момент времени t> сигнал 24 подается на нижние,по фиг. 1 входы схем «И»

4, 5, 6, 7 и, проходя через схему 4, запоминается триггером 9.

В момент 4 перед началом кодо25 вых последовательностей 25, несущих информацию о вероятностях ьтр изнаков, блок декодирования 22 вырабатывает сигнал установки нуля распределителя 13.

Сигнал «1» появляется на первом (левом по з0 фиг. 1) выходе распределителя 13. Происходит опрос триггера 9 с помощью схемы 14 и установка в нуль триггера 12. Так как триггер 9 запомнил сигнал «1», ранее поступивший с выхода блока 8, то на выходе схемы «И» 14 появится сигнал «1», который, пройдя через схему «ИЛИ» 18, поступит в решающий блок 19. Этот сигнал разрешает обработку приходящей в момент времени 4 первой кодовой последовательности 25, несу40 щей информацию о вероятности признака.

В момент времени t4 поступает сигнал 23 и продвигает сигнал «1» с первого выхода распределителя 2 на второй выход, Этот сигнал подается на вход схемы «И» 5.

По окончании (в момент времени 4) кодовой последовательности 25 блок 21 выдает импульс на продвижение распределителя 13.

Сигнал «1» с его первого выхода перемещается на второй. Происходит установка в нуль триггера 9 и опрос триггера 10 с помощью схемы «И» 15.

Поскольку на вход триггера 10 сигнал 24 не поступал, что соответствует отсутствию метки оперативной информации, то на входе

56 схемы совпадения 15 сигнал «1» будет отсутствовать, и на ее «0», В результате со схемы «ИЛИ» 18 на вход решан щего блока 19 сигнал не поступит, что запретит обработку второй кодовой последо60 вательности.

Поступающие вслед за этим сигналы выполняют аналогичные функции:

477421

23 — продвигает сигнал «1» со второго на третий выход распределителя;

31 — устанавливает в нуль триггер 10 и опрашивает триггер 11 с последующей выдачей сигнала с выхода схемы «И» 16 через схему «ИЛИ» 18 на решающий блок 19.

Таким образом, процесс записи оперативной информации в триггеры 9, 10, 11, 12 с последующим ее считыванием и выдачей в решающий блок будет циклически повторяться.

При работе устройства неточность ориентации дисков относительно друг друга и неточность нанесения кодовых меток оперативной информации приводит к изменению временного опережения сигнала 31 сигналом 24, Поскольку текущие сигналы 24 запоминаются триггерами, то временное опережение сигналом 24 сигнала 31, производящего считывание информации с триггеров, не нарушает соответствия между метками оперативной информации и кодовыми последовательностями постоянной информации. Величина допустимого опережения сигнала 31 сигналом 24 зависит от количества элементов схемы.

Неточность ориентации дисков относительно друг друга и неточность нанесения меток оперативной информации не снижает надежности работы устройства.

Предмет изобретения

Диагностическое вычислительное устройство, содержащее блоки кодовых меток постоянной и оперативной информации, решающий блок, отличающееся тем, что, с целью

6 повышения надежности работы устройства, в него введены блок выработки синхросигнала, распределители, счетный вход первого из которых подключен к выходу блока тактовых меток и ко входу первого блока декодирования, выход которого подключен к управляющему входу первого распределителя, первая группа схем «И», первые входы которых подключены к соответствующим выходам перво1о ro распределителя, а вторые входы объединены и подключены к выходу блока кодовых меток оперативной информации, триггеры, первые входы которых подключены к выходам соответствующих схем «И» первой груп15 пы, вторая группа схем «И», первые входы которых подключены к единичным выходам соответствующих триггеров, второй вход р-й схемы «И» второй группы, кроме первой схемы «И», подключен ко второму .входу (р — 1)-го триггера и к р-му выходу второго

20 распределителя, второй вход первой схемы «И» второй группы подключен ко второму входу последнего триггера и к первому выходу второго распределителя, выходы схем

«И» второй группы соединены соответственно

25 со входами схемы «ИЛИ», выход которой соединен с первым входом решающего блока, ко второму входу которого подключен выход блока кодовых меток постоянной информации и вход блока выра бопки синхросигнала, вызО ход которого соединен со счетным входом второго распределителя, управляющий вход второго блока декодирования, вход которого соединен с выходом которого подключен и выходу блока кодовых меток постоянной ин35 формации, 477421!!!

27) †.! — I—

28 ) Составитель А, Жеренов

Техред М. Семенов

Редактор Б. Нанкина

Корректор Е. Рожков»

Заказ 7690 Изд. № 1659 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, 5К-35, Раушская наб,. д. 4/5

МОТ, Загорский филиал Г! !!

Ь

И «!

2

1 (!

1 1

1 !! 1