Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ ii 477464

Союз Советских

Социалистииесних

Республик

ИЗОБРЕТЕН ИЯ

К АВ7ОРСХОМУ СВИДИЕЛЬСТВУ (6I) Дополнительное к авт. свид-ву— (22) Заявлено 27.03.74 (21) 2008982/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 15.07.75. Бюллетень № 26

Дата опубликования описания 06.12.76 (51) М. Кл. С 11с 15/00

Гааудвратввиный камитвт

Саввта Миниатрав СССР

IID двлвм изабрвтвний и аткра1ти» (53) УДК 628.327.66 (088.8) (72) Авторы изобретения

Е. П. Балашов, В. В. Васильев и T. Э. Темирханов (71) Заявитель

Ленинградский ордена Ленина электротехнический институт имени Ульянова (Ленина) (54) ЛОГИЧЕСКОЕ ЗАПОМИ НАЮЩЕЕ УСТРОЙСТВО

Предлагаемое изобретение относится к области запоминающих устройств (ЗУ) и может быть применено в цифровых вычислительных машинах.

Известно на ЗУ МОП-транзисторах, выполняющее функции записи, хранения и считывания с разрядной организацией структуры.

Недостатком таких ЗУ является ограничевность функциональных возможностей.

Целью предлагаемого изобретения является расширение функциональных возможностей ЗУ, т. е. реализация в ЗУ кроме функций записи, хранения и считывания широкого набора логических операций.

Предлагаемое устройство отличается тем, что содержит управляющие шины, шину «разрешение записи» и управляющие логические схемы по числу блоков памяти, состоящие из схем «И», «ИЛИ» и «НЕ», причем одни из входов блоков памяти подключены к выходу первой схемы «ИЛИ», входы которой подключены к выходам первой и второй схем «И», первые входы которых подключены к соответствующим управляющим шинам.

Второй вход первой схемы «И» подключен к,выходу регистра входного слова, а второй вход второй схемы «И» подключен к выходу регистра входного слова чврез схему

«НЕ». Другие входы блоков памяти подключены к выходу второй схемы «ИЛИ» через третью схему «И», один из входов которой подключен к шине «разрешение записи», 5 входы второй схемы «ИЛИ» подключены соответственно к выходам четвертой .и пятой схем «И», первые входы которых подключены к соответствующим управляющим шинам, второй вход четвертой схемы «II» подключен

10 к выходу регистра входного слова, а второй вход пятой схемы «И» подключен к выходу регистра входного слова через схему «НЕ».

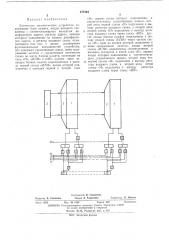

На чертеже, показана функциональная схема логического запоминающего устройст1ь ва (ЛЗУ).

ЛЗУ содержит накопитель, состоящий из блоков памяти 1 со встроенными дешифраторами адреса 2, регистр адреса 3, схемы «И», 4, схемы «ИЛИ» 5 и 6, схемы «И» 7 — 10, 2о схемы «НЕ» 11, регистр входного слова 12, шину «разрешение записи» 13 и управляющие шины 14 — 17. Входы блоков памяти соединены с выходами дешифраторов адреса 2, входы которых подключены к выходам реги25 стра адреса 3. Один из входов каждого блока памяти 1 подключен к выходу схемы

«ИЛИ» 5, входы которой подключены к вы ходам схем «И» 7 и 8, первые входы которых подключены к управляющим шинам 14 m 15, зо а второй вход схемы «И» 7 подключен к вы3 ходу регистра входного слова 12. Второй вход схемы «И» 8 подключен к выходу регистра входного слова 12 через схему «НЕ» 11, другой вход каждого блока памяти 1 подключен к выходу схемы «ИЛИ» 6 через схему «И» 4, а входы схемы «ИЛИ» 6 подключены к выходам схем «И» 9 и 10,,первые входы которых подключены к управляющим шинам 16 и 17, а второй вход схемы «И» 9 подключен к выходу регистра входного слова 12. Второй вход схемы «И» 10 подключен к выходу регистра входного слова 12 через схему «НЕ» 11,,причем один из входов схемы «И» 4 подключен к шине «разрешение записи» 13, общей для всех блоков памяти 1.

Расширение функциональных возможностей ЛЗУ обеспечивается при наличии в составе блоков памяти схемы записи с упра вляющим входом «разрешение записи», зависящим от входного сигнала. Для обеспечения этой возможности структурная организация блоков памяти должна обеспечить сохранение внутреннего состояния элемента памяти при некотором значении сигнала «разрешение записи» (например, при значении О). Полагая, что это условие выполняется, можно получить аналитическое выражение функции переходов произвольного элемента памяти, входящего в состав субсистемы в виде

q,. (/+1) = q,. (t) R Я Vq,. (t) А(/) R(t),, iу S (t) R (t) А (t), (1) где q,(t+1) — состояние элементов памяти в момент времени (t+1), q;(t) — состояния элемента памяти в момент времени 1, R(t) — сигнал «разрешение записи», А (t) — адресный сигнал, S(t) — входной сипнал.

В режиме хранения А (t) = О выражение (1) .приводится к виду

Ч (/+1) = / (/).

При обращении к элементу памяти

А (/) = 1 выражение обращается в

q,. (1+1) = q,. (t) R(t) 5(() R(t), (2)

В режиме записи R(/) = 1 функция переходов (1) имеет вид q,. (t+1) = q; (t).

Отсюда видно, что функция переходов элемента памяти, входящего в состав блоков памяти, представленная в виде (1), описывает все режимы работы элемента памяти в составе обычного оперативного запоминающего устройства. Из выражения (2) очевидно, что состояние, в которое переходит элемент памяти в режиме записи, есть функция от трех переменных

q;(t+1) = ЫЯ; (/); / (Н (З)

Отождествляя в нутреннее состояние элемента памяти в момент времени 1 со з начением некоторой переключательной функции от двоичной переменной y(t) и задавая еигналы на входах субсистемы R u S как пере477464

4 ключательные функции от входной переменной х(/), выражение (2), преобразуется к виду

q,, (/+ 1) = (q) (ó) ° R (x), S (x) R (x) ) (4)

Функция переходов, представленная в виде (4), становится функцией от двух двоичных переменных x(t) и y(1). Выражения этой функции определяются видом функций гр(у), R (x); S (x) . Функции R (x) и S (x) реализуются с помощью управляющих логических схем. Управляющие сигналы г! — г4 на управляющих шинах 14 — 17 задают вид функций

R(x) и S(x). С учетом управляющих сигналов г, выражение (4) приводится к виду:

q, (г+1) — q,(y) (rçx . г4х) (r!x г,х) (г,х ., г,х) . (5)

Различные выражения для функции (5) при всех комбинациях управляющих сигналов r,, показаны в таблице.

Выполняемая логическая операция при

25 Д о о п.п.

Г!, >2, f3, Т(У) =У р(у) =у

УЛх

g х- -у хЛУ у у.х у Vx х

g х- -у

g 7х

45 Работа ЛЗУ поясняется на примере реализации логической операции «ИМПЛИКАЦИЯ» между двумя двоичными переменными х и у, одна из которых, например х, хранится на регистре входного слова, а дру50 гая — у, в ячейке памяти накопителя. Для выполнения заданной логической операции необходимо, чтобы комбинации сигналов на управляющих шинах были следующими: на шинах 15 и 17 сигнал имеет единичное зна55 чение, а на шинах 14 и 16 он равен О.

При такой .комбинации управляющих сигналов и при наличии сигнала па шине «разрешение записи» 13 содержимое регистра

60 входного слова 12 через схемы «НЕ» 11, схемы «И» 8 и 10, схемы «ИЛИ» 5 и 6 и схемы «И» 4 передается в ячейку памяти субсистем, где хранится операнд у. Результат операции получается после окончания режима

65 записи, 1

30 2

4

6

35 8

11

12

13

14

000!

0011

0101

0111

1001

1011

1100 !

I0I

Ill!

g хЛУ х(у

g х/у х у

gхЛУ у õ

g х/у у -х

477464

Предмет изобретения

Составитель В, Гордонова

Техред 3. Тараненко

Корректор Л. Орлова

Редактор Е. Семанова

Заказ 3656 Изд. Ко 1638 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

МОТ, Загорский филиал

Логическое запомингиощее устройство, содержащее блок памяти, входы которого соединены с соответствующими выходами дешифраторов адреса, регистр адреса, выходы которого подключены ко входам дешифраторов адреса, и регистр входного слова, отлича ощееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит управляющие шины, ши ну «разрешение записи» и управляющие логические схемы по числу блоков памяти, состоящие из схем «И», «ИЛИ» и «НЕ», причем одни из входов блоков памяти подключенных к выходу первой схемы «ИЛИ», входы которой подключены к выходам первой и второй схем

«И», первые входы которых подключены к соответствующим управляющим шипам, второй вход первой схемы «И» подключен к выходу регистра входного слова, а второй вход второй схемы «И» подключен к выходу регистра входного слова через схему «НЕ», другие входы блоков памяти подключены к выходу второй схемы «ИЛИ» через третью схему «И», оди н из входов которой подключен к

1О шине «разрешение записи», входы второй схемы «ИЛИ» подключены соответственно к выходам четвертой и пятой схем «И», первые входы которых подключены к соответствующим управляющим шинам, второй вход чет15 вертой схемы «И» подключен к выходу регистра входного слова, а второй вход пятой схемы «И» подключен к выходу регистра входного слова через схему «НЕ».