Резирвированный делитель-формирователь

Иллюстрации

Показать всеРеферат

ОП ИCA-Н-ИЕ

ИЗОБРЕТЕНИЯ (п1 477545

Союз Советских

Социалистнческии

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 14.12.73 (21) 1976751/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 15.07.75. Бюллетень № 26

Дата опубликования описания 03.10.75 (51) М. Кл. Н 03k 23, 02

Государстоеннык комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621 374 4 (088.8) (72) Автор изобретения

И. И. Нисенбойм (71) Заявитель (54) РЕЗЕРВИРОВ АННЪ|Й ДЕЛИТЕЛЬ-ФОРМИРОВАТЕЛЬ

Изобретение относится к вычислительным системам с резервированием и может быть применено в резервированных устройствах деления частоты и формирования тактовых импульсов, Известен резервированный делитель-формирователь, содержащий счетчик на Д-триггерах, выходы которых подключены ко входу логического элемента.

Однако в известном устройстве не происходит восстановления синфазной работы делителя при себе одного из резервных каналов и отказе другого, что в итоге понижает надежность работы делителя частоты.

Для повышения надежности работы в предлагаемый делитель-формирователь введены последовательно соединенные RS-триггер и дополнительный Д-триггер, подключенные к выходу упомянутого счетчика, и дополнительный логический элемент «ИЛИ», один вход которого через мажоритарный элемент соединен с выходом дополнительного Д-триггера, другой вход — с выходом упомянутого логического элемента, а выход — с R-входом RSтриггера.

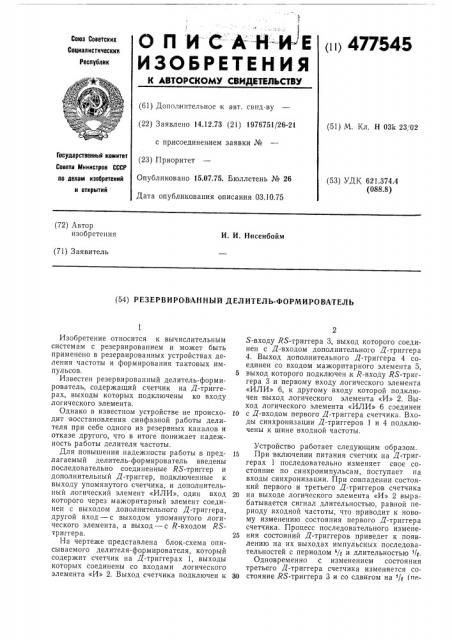

На чертеже представлена блок-схема описываемого делителя-формирователя, который содержит счетчик на Д-триггерах 1, выходы которых соединены со входами логического элемента «И» 2, Выход счетчика подключен к

S-входу RS-триггера 3, выход которого соединен с Д-входом дополнительного Д-триггера

4. Выход дополнительного Д-триггера 4 соединен со входом мажоритарного элемента 5, 5 выход которого подключен к R-входу RS-триггера 3 и первому входу логического элемента

«ИЛИ» 6, к другому входу которой подключен выход логического элемента «И» 2. Выход логического элемента «ИЛИ» 6 соединен

10 с Д-входом первого Д-триггера счетчика. Входы синхронизации Д-триггеров 1 и 4 подключены к шине входной частоты.

Устройство работает следующим образом.

15 При включении питания счетчик на Д-триггерах 1 последовательно изменяет свое состояние по синхроимпульсам, поступает на входы синхронизации. При совпадении состояний первого и третьего Д-триггеров счетчика

20 на выходе логического элемента «И» 2 вырабатывается сигнал длительностью, равной периоду входной частоты, что приводит к новому изменению состояния первого Д-триггера счетчика. Процесс последовательного измене25 ния состояний Д-триггеров приведет к появлению на их выходах импульсных последовательностей с периодом 4/< и длительностью /g.

Одновременно с изменением состояния третьего Д-триггера счетчика изменяется со30 стояние RS-триггера 3 и со сдвигом на /f (пе477545 П р едмет и з обер етен и я

Составитель М. Аудрннг

Техред Т. Курнлко

Корректор Е. Хмелева

Редактор С. Байкова

Заказ 2408/8 Изд. И 1622 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 риод входной частоты) сработает дополнительный Д-триггер 4. Таким образом, изменение состояния дополнительного Д-триггера 4 совпадает с изменением состояния логического элемента «И» 2 и не влияет на процессы деления и формирования в случае синфазной работы резервных каналов; при этом RS-триггер 3 изменяет свое состояние дважды — вначале по сигналу с выхода счетчика 3, затем по сигналу с мажоритарного элемента 5.

При расфазировке каналов первый сработавший RS-триггер 3 и включенный последовательно с ним дополнительный Д-триггер 4 сохраняют свое состояние до тех пор, пока не сработают аналогичные каскады в другом канале. На выходе мажоритарных органов 5 появляются сигналы, перебрасывающие RSтриггеры 3 в исходное состояние и формирующие запрет по Д-входам первых Д-триггеров

1. При этом эти Д-триггеры 1 одновременно со сдвигом на период входной частоты повторяют состояние своего Д-входа, а далее процесс синфазной работы обеспечивается аналогично вышеописанному.

Очевидно, что при отказе двух из резервных каналов, сигнал на выходе мажоритар5 ных органов отсутствует и они не влияют на работу исправного канала.

10 Резервированный делитель-формирователь, содержащий счетчик на Д-триггерах, выходы которых подключены ко входу логического элемента, отличающийся тем, что, с целью повышения надежности работы, в него

15 введены последовательно соединенные RSтриггер и дополнительный Д-триггер, подключенные к выходу упомянутого счетчика, и дополнительный логический элемент «ИЛИ», один вход которого через мажоритарный эле20 мент соединен с выходом дополнительного Дтриггера, другой вход — с выходом упомянутого логического элемента, а выход с К-входом RS-триггера.