Устройство для преобразования сигнала

Иллюстрации

Показать всеРеферат

тпт 477549

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Зависимое от авт. свидетельства (22) Заявлено 12.04,73 (21) 1906139/26-21 с присоединением заявки № (5I) М. Кл. H 04l 3/02

Н 04Ь 1/10

Совета Министров СССР ло делам изобретений и открытий

Опубликовано 15.07.75. Бюллетень № 26

Дата опубликования описания 11.11.75 (53) УДК 681.3.055 (088.8) (72) Авторы изобретения

Л. A. Мироновский и В. А. Слаев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ СИГНАЛА

Государственный комитет (32) Пр р

Изобретение относится к области радиотехники. Устройство может быть использовано для подавления помех при передаче сигналов.

Известны устройства для преобразования сигнала, используемые для получения сигнала с постоянной дисперсией.

Недостатком известных устройств является отсутствие возможности коррекции помех при приеме сигнала, обладающего информационной избыточностью.

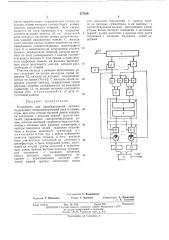

В целях повышения точности передачи сигналов в предлагаемое устройство введены блок диагностики, состоящий из делителя и дешифратора, и блок коррекции помех, состоящий из группы вентилей и вычитающих узлов. При этом выходы входных сумматоров соединены с входами делителя, выход делителя через дешифратор соединен с управляющими входами вентилей блока коррекции, сигнальные входы которых подключены к выходу одного из входных сумматоров, а выходы этих вентилей соединены с соответствующими входами вычитающих узлов. Вторые входы вычитающих узлов подключены к выходам первой группы вентилей, а выходы этих узлов соединены с входами выходных линий задержки.

На чертеже показана структурная схема предлагаемого устройства.

Принятый сигнал p(/) продолжительности

Т, состоящий из и+2 участков, два из которых являются избыточными, поступает на вход линии задержки 1. С и+2 отводов линии задержки сигналы подаются на сигнальные входы вентилей 2. Синхронизирующее устройство

3 открывает эти вентили на время Т/тг+2 в конце интервала Т. Участки сигнала у(т) с выходов вентилей через аттенюаторы 4 поступают на входы сумматоров 5. Таким образом, на выходе сумматоров 5 образуются два сигнала рассогласования длительности Т/и+2, равной длительности одного участка, представляющие собой взвешенную с различными весовыми коэффициентами сумму n+2 участков принятого сигнала 9(). Коэффициенты аттенюаторов подбираются так, чтобы сигнал рассогласования с выхода одного из сумматоров 5, повторял форму напряжения помехи, а сигнал с выхода другого сумматора 5 был больше его в число раз, равное номеру участка сигнала, который поражен помехой. В частности, когда помеха в сигнале у(т) отсутствует, оба сигнала рассогласования равны нулю.

Сигналы рассогласования с выходов сумматоров 5 подаются на блок диагностики б, именно на делитель 7. С выхода делителя напряжение, пропорциональное номеру участка, пораженного помехой, проходит на вход де30 шифратора 8, имеющего и+2 выхода. Дешиф477549

Предмет изобретения

Составитель С. Поликарпов

Техред T. Курилко

Корректоры: А. Денискина и А. Галахова

Редактор Т. Юрчикова

Заказ 2413/11 Изд. № 1619 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-З5, Раушская наб., д. 4)5

Типография, пр. Сапунова, 2 ратор вырабатывает управляющий сшнал на выходе, номер которого соответствует номеру участка, пораженного помехой. Этот сигнал подается на блок коррекции 9 и открывает соответствующий вентиль 10, на сигнальный вход которого поступает сигнал рассогласования, равный напряжению помехи. С выхода этого вентиля сигнал помехи подается на вход вы читаемого соответствующего вычитающего узла 11 и вычитается из напряжения участка сигнала, пораженного помехой, которое поступает на вход уменьшаемого с выхода соответствующего вентиля 2. Тем самым осуществляется коррекция помехи, на выходах вычитающих узлов получаются участки сигнала y(t), 15 свободные от помехи.

Участки сигнала с выходов вычитающих узлов поступают на входы выходных линий задержки 12, каждая из которых задерживает сигнал на время iT п+2. С выходов линий за- 20 держки участки сигнала, задержанные таким образом, линейно складываются на выходном сумматоре 13, на выходе которого получается сигнал x(t), отличающийся от g(t) отсутствием помехи. 25

Устройство для преобразования сигнала, содержащее синхронизирующий узел и сумма- З0 торы, при этом отводы входной линии задержки соединены с входами первой группы вентилей, управляемых синхронизирующим узлом, выходы вентилей соединены через аттенюаторы с входами двух входных сумматоров, а З5 выходы выходных линий задержки подключены к входам выходного сумматора, о тл и ч а ю щ е е с я тем, что, с целью повышения точности передачи сигнала, в него введены блок диагностики, состоящий из делителя и 40 дешифратора, и блок коррекции помех, состоящий из второй группы вентилей и вычитающих узлов, причем выходы входных сумматоров соединены с входами делителя, выход которого через дешифратор со- 45 единен с управляющими входами вентилей второй группы, сигнальные входы этих вентилей подключены к выходу одного пз входных сумматоров, а их выходы — к соответствующим входам вычитающих узлов, вторые входы которых соединены с выходами первой группы вентилей, а выходы этих узлов соединены с входами выходных линий задержки.