Приемный стартстопный распределитель

Иллюстрации

Показать всеРеферат

! ОПИСАНИЕ

ИЗОБРЕТЕ Н ИЯ пц 47755I

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«« « (61) Дополнительное к авт. свеид-ву (22) Заявлено 13.08.73 (21) 1954898/26-9 с присоединением заявки № (23) Приоритет

Опубликовано 15.07.75. Бюллетень № 26

Дата опубликования описания 11.11.75 (51) М. Кл. Н 041 13/14

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.394.61 (088.8) (72) Автор изобрстения

Г. C. Долгополов (71) Заявитель (54) ПРИЕМНЫЙ СТАРТ-СТОПНЫЙ РАСПРЕДЕЛИТЕЛЬ

Изобретение относится к области дискретных систем связи.

Известен приемный старт-стопный распределитель, содер>кащий задающий генератор, схемы И, делитель, триггер, формирователь и регистр ком би и ацн й.

При использовании в линиях связи нестабильных генераторов или в случае неточной настройки частоты приемного распределителя уменьшается достоверность принимаемого сообщения вследствие уменьшения исправляющей способности приемного устройства. В известном распределителе для повышения достоверности принимаемого сигнала старт-стопнь.х передач оператор вынужден вручную изменять модуль делителя с помощью переключателей.

В целях расширения функциональных возмо>кностей путем автоматизации процесса изменения модуля делителя в предлагаемый р аспределитель введены дешифр атор совпадения, реверсивный счетчик и дешифратор записи. Сигнал «Пуск» через дешифратор записи, реверсивный счетчик, первый вход и выход дешифратора совпадения подается одновременно к входу формирователя и входу делителя, выход которого подключен к второму входу дешифратора совпадения.

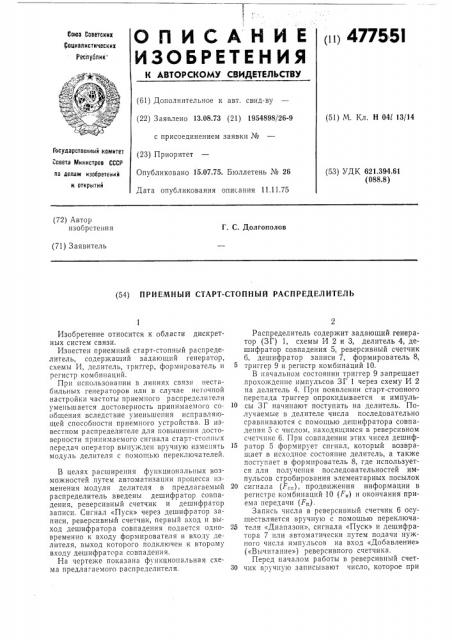

На чертеже показан- функциональная схема предлагаемого распределителя.

Распределитель содержит задающий генератор (ЗГ) 1, схемы И 2 и 3, делитель 4, дешифратор совпадения 5, реверсивный счетчик б, дешифратор записи 7, формирователь 8, 5 триггер 9 и регистр комбинаций 10.

В начальном состоянии триггер 9 запрещает прохо>кдение импульсов ЗГ 1 через схему И 2 на делитель 4. При появлении старт-стопного перепада триггер опрокидывается и импуль10 сы ЗГ начинают поступать на делитель. Получаемые в делителе числа последовательно сравниваются с помощью дешифратора совпадения 5 с числом, находящимся в реверсивном счетчике 6. При совпадении этих чисел дешифратор 5 формирует сигнал, который возвращает в исходное состояние делитель, а также поступает в формирователь 8, где используется для получения последовательностей импульсов стробирования элементарных посылок

20 сигнала (F„), продвижения информации в регистре комбинаций 10 (F,) и окончания приема передачи (F,).

Запись числа в реверсивный счетчик 6 осуществляется вручную с помощью переключа2ä теля «Диапазон», сигнала «Пуск» и дешифратора 7 или автоматически путем подачи нужного числа импульсов на вход «Добавление» («Вычитание») реверсивного счетчика.

Перед началом работы в реверсивный счет30 чик вручную записывают число, которое при

47755f

ß äïàçîí Ф

-„Пусл ,Я пиление б — —, ынилплие

i 5) Бииа@ии

Жчлибыхпд ним3инпции пар аллепьнпй ферм

Составитель И. Черняк

Техред Т. Курилко

Редактор T. Юряикова

1(орректоры: А. Денискина и А. Галахова

Заказ 2413/12 Изд. М 1619 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

rto делам изобретений и открытий

Москва, Я(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 перемножении на длительность периода ЗГ приблизительно дает значение длительности элементарной посылки сигнала. В дальнейшем, подавая импульсы на вход «Добавление» («Вычитание») реверсивного счетчика, добиваются того, чтобы длительности элементарных посылок приемного и передающего распределителей отличались одна от другой на величину, не превышающую периода ЗГ. Эти импульсы можно получить, например, с выхода специального устройства определения расхождения частот приемного и передающего распределителей (частотный или фазовый дискриминатор).

С помощью импульсов F«, поступающих на вход схемы И 3, производится определение полярности элементарных посылок приходящего сигнала. Сигнал F, используется для продвижения «1» и «О» в регистре комбинаций 10, а сигнал F„ — для установки триггера

9 в исходное состояние.

Предмет изобретения

Приемный старт-стопный распределитель, содержащий задающий генератор, подключенный через первый вход и выход первой схемы

И к первому входу делителя, к второму входу которого через первые вход и выход триггера подключен первый выход формирователя, под5 соединенного вторым и третьим выходами соответственно к первому входу второй схемы

И и первому входу регистра комбинаций, выход которого является выходом приемного старт-стопного распределителя, причем сигнал

10 старт-стопного перепада через вторые вход и выход триггера подсоединен к второму входу первой схемы И, а информационный сигнал через второй вход и выход второй схемы И подключен к второму входу регистра комбина15 ций, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дешифратор совпадения, реверсивный счетчик и дешифратор записи, причем сигнал «Пуск» через дешифратор записи, 20 реверсивный счетчик, первый вход и выход дешифратора совпадения подается одновременно к входу формирователя и третьему входу делителя, выход которого подключен к второму входу дешифратора совпадения.