Управляющий процессор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11) 47829 6

Гасударственный квинтет

Свввтв Мнннетрев СССР в делам нзебретеннй

H DTKPblTNH

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (61) Зависимое от авт. свидетельстваI (22) Заявлено 17.07.72 (21) 1811881/18 24 с присоединением заявки №(32)ПриоритетОпубликовано 25.07.75.Бюллетень №27.l (51) М, Кл. (О 06 1/00 (53) УДК628.327.6 (088.8), Дата опубликования описания 05.08.75

В. Г. Воржев, В. Г. Колосов и С. П. Некрасов (72) Авторы изобретения (71) Заявитель Ленинградский ордена Ленина политехнический институт им. М. И. Калинина (54) УПРАВЛЯЮЩИЙ ПРОЦЕССОР

1

Изобретение относится к вычислительной технике и может найти применение в системах автоматизации производственных процессов, а также в составе информационных систем для приема и первичной обработки данных, поступающих в аналоговой форме. .з

Известны и широко применяются управляющие процессоры, имеющие в своем составе преобразователь "напряжение-код, коднапряжение для приема аналоговых сигналов. от объекта и формирования выходных аналоговых сигналов процессора. Известны также процессоры, в которых часть арифметических операций выполняется непосредственно в преобразователе напряжениекод, код-напряжение или so входных цепях его.

Цель изобретения - упрощение устройства и повышение его быстродействия.

Достигается это благодаря тому, что один из выходов аналогового запоминаю щего блока соединен с коммутатором входных сигналов, выходы которого подключейы ко входам сумматоров, а выходы третье1

2 го и четвертого сумматоров подсоединены соответственно к входам первого и второго сумматоров.

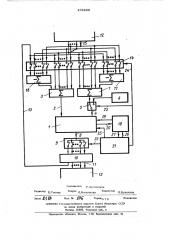

На чертеже приведено предлагаемое

5 устройство.

Процессор содержит преобразователь

"код-напряжение, напряжение -код" 1. Один иэ его аналоговых входов связью 2 соединен с выходом сумматора 3. Другой анар логовый вход преобразователи связью 4 соединен с переключателем 5 и далее с источником эталонного напряжения 6 и выходом сумматора 7. Аналоговый выход преобразователя по связи 8 через комму1а татор 9 соединен с аналоговым запомина-. ющим блоком 10. Аналоговый запоминающйй блок связями 11 соединен с объектом 12, а связью 13 - с коммутатором входных сигналов 14. Последний в свою з0 очередь, связан с объектом (связь 15) и с сумматорами 3, 7 и сумматорами 16,, 17. Процессор содержит также цифровой запоминающий блок 18, который имеет связи 19,, 20 для обмена кодами с преоб-

25 разователем. .Работа процессора органи478296

3 .зкется устройством управления 21, име.ющим связи 22, 23, 24 . с управляющи- ми входами коммутаторов и ключа, связи t ,25, 26 для посылки сигналов в преобра» зователь и цифровой запоминающий блок, 5

ja также связь 27 для приема информации ! из цифрового запоминающего блока.

Работа устройства в динамике происхо1 дит следующим образом.

Программа в командах хранится в циф-, 10 ровом запоминающем блоке 18, который также служит для хранения промежуточных .результатов и констант.

Команды из цифрового запоминающего

;блока но связи 27 поступают в устройст во управления 21, где преобразуются в управляющие сигналы, поступающие в связи 22-26, Аналоговый запоминающий блок 10 обеспечивает подачу на объект определенныэ ® уровней напряжений, величина которых определяется периодически сигналом по свя зи 8 из преобразователя 1 через коммутатор 9. Аналоговый запоминающий блок используется также для хранения некоторых промежуточных результатов, поступающих затем по связи 13 для дальнейших вычислений.

Взаимодействие блоков процессора и порядок подключения коммутаторов приме.,нительно к процессу выполнения отдельных

1 команд происходит следующим образом.

Команда вычисления отношения алгебраических сумм аналоговых сигналов с получением ответа в виде кода выполняется следующим образом.

Устройство управления по связи 24обеспечивает замыкание определенных ключей в коммутаторе 14 так что необходимый набор аналоговых сигналов (их сумма обозначается в дальнейшем X Д ) постуL пает на вход сумматора 3, сигналы Д поступают на вход сумматора 16, сигналы

1 А — на вход сумматора 7 и сигналы

- на вход сумматора 17. Переклю6 чатель 5 по связи 23 подключает вход 4 к выходу сумматора 7.

В преобразователь по связи 25 подается сигнал "преобразовать напряжение в код . Результат преобразования в виде кода по связи 20 подается в цифровой запоминающий блок.

В преобразователе процесс преобразования напряжение-код завершается в момент, когда

В + где К - величина результата в форме кода, 4

0 — напряжения на входах преобра12 4 зователя по связям 2 и 4.* !

Таким образом, рассмотренная команда обеспечивает вычисление.: по формуле

ХА„-:.А„ ЕА),- XAL

Частным случаем этой команды явля-, ется вычисление отношения у 4> (в

А> этом случае коммутатор 14 подает только! сигналы A u A соответственно, в сумматоры 3 и 7).

Команда алгебраического сложения аналоговых . сигналов с преобразованием в код выполняется аналогично описанной, толь ко переключатель 5 по связи 23 устанавливается в такое положение, что он подключает вход 4 преобразователя к источнику эталонного напряжения 6.

Частным случаем этой команды явля- .

1 ется преобразование аналогового сигнала в код.

Команда умножения алгебраической суммы аналоговых сигналов на величину, представленную кодом с формированием ответа в виде аналогового сигнала, выполня-I ется следующим образом. 1

Коммутатор 14 обеспечивает подачу суммы сигналов Д на входы сумматора

7 и суммы сигналов gA на входы сумматора 17. Переключатель 5 подключает вход 4 к сумматору 7, в преобразователь поступает сигнал "преобразовать код в напряжения".

Преобразователь завершает работу в момент, когда IJ = КО

1 1 где U - напряжение на выходе преобразователя, а К - множитель в виде кода.

Таким образом, в этой команде производится вычисление по формуле (хА„-"., К = ()

Частным случаем этой команды явля- ется умножение аналогового сигнала на величину, представленную кодом.

Команда преобразователя кода в напряжение осуществляется аналогично рассмотренной с той разницей, что переключатель

5 подключает вход 4 к источнику эталонного напряжения 6.

Таким образом, в процессоре можно выполнить все четыре арифметических действия. Однако часть операндов при этом должна быть. представлена аналоговыми сигналами. Для обеспе«

478296

Дополнительным достоинством предлагаемого процессора является малое число управляющих сигналов (на входы коммутаторов и переключателя), за счет возбуждения которых могут выполняться различные

I команды и программы.

Предмет изобретения

Управляющий процессор, содержащий преобразователь, первый вход которого подключен к выходу первого сумматора, а второй вход через переключатель — к выходу второго сумматора и к источнику эталонного напряжения, третий вход и первый выход преобразователя соединены с цифровым запоминающим блоком, второй выход через коммутатор выходных сигнаж>в подключен к аналоговому запоминающему блоку, блок управления соединен с преобразователем, коммутаторами входных и выходных сигналов, переключателем и цифровым запоминающим блоком, о т л и ч а ю щ и йс я тем, что, с целью упрощения устройства и повышения его быстродействия один из выходов аналогового запоминающего блока соединен с коммутатором входных сигналов, выходы которого подключе- I ны к входам сумматоров, а выходы третье-: го и четвертого сумматоров подсоединены: (( соответственно к входам первого и второ-, го сумматоров. чения большей гибкости процессора при реализации программ в нем предусмотрена, возможность запоминания результатов . в

r аналоговой форме с последующей подачей - .

:их по связи 13 для дальнейших вычисле5, ний.

Например, умножение двух величин К

: и К, представленных кодами, выполняет-; ! ся в два этапа. Сначала величина К1 пре- 10 . образуется в напряжение и запоминается, затем умножается на:;К z как это уже было рассмотрено.

Все вычислительные операции выполня;:ются без специального арифметического устройства с помощью преобразователя, аналогового запоминающего блока и комму . таторов, которые обязательно входят в состав управляющего процессора для связи с щ объектом. Тем самым достигается экономия оборудования и повышается надежность процессора..

По быстродействию процессора также достигается определенный выигрыш, потому что совмещаются процессы вычисления и преобразования в цифровой код. Кроме того, операции умножения и деления выполняются за время одного преобразования, что обычно по количеству необходимых так- З0 тов работы много выгоднее, чем при реапгзации этих операций в арифметическом устройстве с цифровыми сумматорами.

478296

Составитель F А ртамонов

Техред Корректор

Л.Каза чкова Л.Брахнина

Редактор . ончар

Заказ g P(Изд. 34 8й ТиРаж6 7 9 Подписное

Предприятие сПатеитэ, Москва, Г-59, Бережковская иаб., 24

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, 113035, Раушская наб., 4