Матричный сумматор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсюа

Социал истичесюа

Республик (11) 4783О4 (61) Дополнительное к авт. свид-ву(22) Заявлено 14.07.72 (21) 1819772/18-24 с присоединением заявки №(23) ПриоритетОпубликовано 25.07. 75,Бюллетень № 27

Дата опубликования описаиия05.08.75 (51) М. Кл. (06f 7/385

Гасударственный нюмнтвт

Савнтв Мнннвтрев СССР нв данам нвобрвтвннй н нткрытнй (53) УДК 681.325.5 (088. 8) К, К. Ешин, С. Б. Петрова, Т. А. Ясногородская, А. К. Заволокин (72) Авторы изобретения и Е. К. Юферова (7 l) Заявитель (54) МАТРИЧНЫЙ СУММАТОР

1

Изобретение относится к вычислительной технике и может быть использовано при разработке арифметических устройств ЭБВМ, предназначенных для ускоренного, сложения чисел, представленных в позиционном коде с произвольным основанием.

Известен матричный сумматор, содержантий регистры групп разрядов суммируемых чисел, выходы которых соединены соответственно со входами матриц значений пере- т0 носов между группами разрядов и матриц сумм групп разрядов, выходы которых подключены соответственно к первым входам схем И, выходы которых соединены со входами выходных регистров групп разрядов 15 сумматора.

Бель изобретения - повысить быстродействие устройства.

Это достигается тем, что выходы регистров групп разрядов суммируемых чисел 20 соединены со входами матриц значений сумм, увеличенных на единипу разряда данной группы, и матриц признаков возможности переносов, выходы которых совмест .но с выходами матриц переносов подклю- 25

2 чены ко входам управляюшей матрищт, выходы которой связаны соответственно со вторыми входами схем И" и со вторыми входами дополнительных схем "И", первые входы которых соединены соответственно с выходами матриц значений сумм, увеличенных на единицу разряда группы, а выходы - с соответствуюшрми входами выходного регистра групп разрядов сумматора.

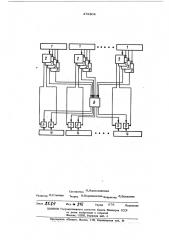

На чертеже представлена функциональная схема матричного. сумматора.

Матричный сумматор состоит иэ регистров 1 групп разрядов суммируемых чисел, матриц 2сумм группы разрядов, матриц 2 значений переносов между груйпами разря: дов, выходного регистра 4 групп разрядов сумматора, схем И 5 и дополнительных схем И 6, матриц 7 значений сумм, увеличенных на единицу младшего разряда данной группы, управляющей матрицы 8 и матриц 9 значений признаков воэможности переносов между группами разрядов.

В исходном состоянии все разряды регистра 1 групп разрядов суммируемых чи4783О4 сел и выходного регистра 4 групп разряO дов сумматора находятся в нулевом состо янии. При поступлении суммируемых чисел

;на регистры 1 с выходов матриц 2 . сни

r маются значения сумм групп разрядов, с выходов матриц 7 — значения сумм, увеличен ных на единииу младшего разряда данной

;группы подаются на схемы И 5 и 6, находящиеся на входе выходного регистра 4.

Одповременно с матриц 3 и 9 сигналы подаются на управляющую матрицу 8, которая согласно заданному алгоритму формиЩ ет на выходе управляющее слово. Выходной регистр устанавливается в состояние, соответствующее результату суммирования исходных чисел по значению выходных сигналов матриц 2 и 7 и управляющего слова.

Предмет изобретения!

Матричный сумматор, содержащий регистры групп разрядов суммируемых чисел выходы которых соединены соответственно со входами матриц значений переносов между группами разрядов и матриц сумм групп разрядов, выходы которых подключе-, 5: ны соответственно к первым входам схем

И, выходы которых соединены со входами выходных регистров групп разрядов сумматора, о т л и ч а. ю шийся тем, что, с целью увеличения быстродействия, выхо®О .ды регистров групп разрядов суммируемых чисел соединены со входами матриц

I значений сумм, увеличенных на единицу разряда данной группы, и матриц признаков возможности переносов, выходы которых совместно с выходами матриц переносов подключены ко входам управляющей матрицы, выходы которой связаны соответственно со вторыми входами схем И и со вторыми, входами дополнительных схем б О И, первые входы которых соединены соответственно с выходами матриц значений сумм, увеличенных на единицу разряда группы, а выходы - с соответствующими входами выходного регистра групп разрядов сумматора.

478304 .Милс с тав кая

Редактор О.Стенина Техреа И.Карандашова 1<ор екто Л.Брахнина орректор

Заказ 4Щ Изд М g Ù Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие <Патент», Москва, Г-59, Бережковская иаб., 24