Устройство для управления процессом

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсних

Совриивестнмеских

)веса убеиек (11) . 478307 (61)Дополнительное к авт. свид-ву(22) Заявлено 17.04.72 (21) 1771715/18 24

/ с присоединением заявки №(51) М. Кл.

G 06 9/06 (53) УДК681.326 (088.8) Гюаударатвеиный квинтет

Cows Миииетрвв СССР ее делам иэебретеиий и вткрытий (23) ПриоритетОпубликовано25 07 75, Бюллетень № 27

Дата опубликования описания 05.08.75

А. А. Авдюхин, В. Г. Колосов, Н. И. Колосова,:В. Ф. Мелехин и С. П. Некрасов (72) Авторы изобретения

I (71) Заявитель Ленинградский ордена. Ленина политехнический институт им. М. И. Калинина (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОРОМ

Изобретение относится к вычислительной технике и может быть использовано для управления работой по программе специали-, зированной UBM или для реализации стандартных подпрограмм в UBN общего назначе- а ния.

Работа UBM по фиксированной программе обычно реализуется с помощью известной структуры, содержащей следующие основные функциональные блоки: 10 распределитель, реализующий работу UBN по программе путем возбуждения одной иэ своих выходных шин (каждой команде в программе соответствует свой выход распределителя); 15 регистр. адреса первой команды, необходимый для образования прямых и инверсных сигналов кода адреса команды {через этот регистр поступает код адреса при безусловных и условных переходах); 20 регистр адреса второй команды, хранящий адрес команды, к которой необходимо обратиться после выполнения стандартной подпрограммы при двухрангавом режиме работы; 25 постоянное запоминающее устройство, в котором хранятся команды; дешифратор адреса команды, на вход которого поступает адрес очередной команды из регистров команд и с выхода кото- . рого возбуждается одна из ячеек постоян- ного запоминающего устройства; регистр кода операции, служашйй для хра нения кодовой части команды, поступающей из постоянного запоминающего устройства; дешифратор кода операции, обеспечивающий выполнение одной команды путем выдачи необходимой последовательности управляющих сигналов; регистр адреса первого операнда, а в случае двух- или трехадресной системы команд еше и регистры адреса второго и третьего операндОв; дешифратор адреса операндов, получающий информацию из регистров адресов опе-: рандов в виде кода "1 иэ 2 в каждом разряде и возбуждающий своим. выходным сигналом одну из ячеек оперативного запоминающего устройства процессора.

4783О7

Каждый из перечисленных блоков является функпионально, а часто и конструктивно самостоятельным устройством, поэтому известные управляющие устройства весьма сложны. б

Бель изобретения - упрощение устройства и повышение его .экономичности.

Достигается это за счет совмещения функций некоторых перечисленных блоков в других блоках. 10

Сущность изобретения достигается в том, что в устройстве каждый выход распределителя подключен к соответствующим входам записи дешифратора адреса операнда. perttcòpoâ адреса операнда, lie- 1и

4 шифратора кода операции и регистров ад . реса команды. Это дает возможность выполнить функции постоянного запоминающего устройства, одного регистра адреса операнда и регистра кода операции в си- gp стеме шин связи распределителя с другими блоками и исключить три упомянутых функциональных блока.

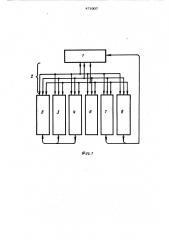

Hs фиг. 1 приведена блок-схема устройства; на фиг. 2 - схема устройства с применением магнитных переключателей тока.

Устройство содержит распределитель 1, построенный, например, по распространенной схеме из счетчика и дешифратора, ре ализующий поочередную передачу импульсов на свои выходные Мины 2; регистры адреса операнда 3, 4, соединенные известным образом с дешифратором адреса операнда; дешифратор адреса . операнда 5, як дешифратор кода операции 6, регистры адреса команды 7, 8, соединенные известным образом с распределителем.

Входы устройства и соответствующие им выходы 9 и 10, 11 и 12, 13 и 14, 15.; и 16, 17 и 18, входы 19, 20 устройства: днодные матрицы 21-28.

Количество регистров адреса операнда зависит от адресности команд и составля-! ет величину от нуля при одноадресной 45 системе до двух при трехадресной. Количество регистров адреса команды равно числу рангов управления в программе.

Изображенная на чертеже структура соответствует трехадресной системе команд SO при двухранговом управлении.

Работает устройство следующим образом. В процессе реализации программы на одной из выходных шин 2 распределителя 1 появляется сигнал. При появлении 55 на выходе распределителя сикнала обеспечивается: запись .в дешифраторе адреса операнда 5 адреса первого операнда, в

I. дальнейшем с помощью дешифратора 5 считывается оперативное запоминающее j 60. 4. устройства (на чертеже не показано); за- пись информации в регистры адреса операнда 3,4, в дальнейшем эта информация бу-, дем переписана в дешифратор адреса операнда 5 дпя; считывания содержимого оперативного запоминающего устройства по соответствующему адресу; запись информации в дешифратор кода операции 6, в дапьнейшем с его выходов будут сформированы сигналы в другие узлы процессора, обеспечивающие выполнение команды; запись циформации в регистры адреса команды 7, 8, в дальнейшем эта информация поступит в распределитель 1 дпя осуществпения условного ипи безусловного перехода в программе, в том числе на новый ранг программы (из подпрограммы ипи в подпрограмму) .

Таким образом, в структуре устройства, исключены постоянное запоминающее уст» ройство, один регистр адреса операнда и регистр кода операции.

Рассмотренная структура устройства мо- жет быть реализована на различных логи- ческих элементах. Однако особенно эффективно; в данном случае применение магнитных переключателей тока в конструктивном оформлении с отверстиями через сердечники, сохраняемыми после заливки элемента компаундом. Параметры импульса тока на выходе распределителя рассчитываются таким образом, чта для подготовки переключателей достаточно, одного витка.

В этом случае цепь каждого из выходов 2 распределителя 1 представляет собой шину, проходящую без промежуточных паек через все необходимые сердечники блоков 5, 3, 4, 6, 7, 8, В схеме (фиг. 2) дешифратор адреса операнда 5 и дешифратор кода операции 6 выполнены двухступенчатыми с диодной матрице й.

Прн работы- схемы подачей импульсов тока па цепи 9-10 обеспечивается начальная установка; по цепи 11-12 - считывание дешифратора кода операции 6; по цепи 13-14 - считывание дешифратора адреса операнда 5; по цепи 15-16 - передача информации из регистра адреса операнда 4 в дешифратор адреса 5; по цепи 1718 - передача информации из регистра адреса операнда 3 в дешифратор адреса операнда 5; по цепям 19-20 - передача адреса команды в распределитель 1 из регистров адреса команды 7 и 8.

По окончании выполнения очередной ко: манды по цепи 9-10 производится установка блоков 3-8 в исходное состояние.

478307

В случае выполнения команд переходов (условного или безусловного) адрес команды, к которой возможен переход, записывается в регистр адреса команды 7. Тогда, если условие перехода выполнено, то в конце выполнения данной команды по цепи 20 считывается содержимое регистра 7 и адрес перехода вводится в распределитель 1.

Если необходимо перейти к выполнению подпрограммы младшего ранга, то для запоминания адреса команды программы старшего ранга, к которой осуществляется

;возврат, этот адрес вводится в регистр адреса команды 8. После выполнения подпрограммы младшего ранга производится д считывание содержимого регистра 8 по цепи 19 и в распределитель 1 вводится адрес возврата.

Запись информации в регистры и дешифраторы осуществляется путем установки ъО определенных сердечников переключателей тока в проводящее направление. При этом готовится единственный путь для тока в цепях считывания этих устройств, опреде- ляемый комбинацией из двух "проводящих сердечников, если устройство имеет два переключателя тока (по одному сердечнику в каждом переключателе, например в блоках 3-6), I

Ф или одним проводящим" сердечником, если устройство имеет один переключатель то- яО ка, (например, в регистрах 7, 8). Это относится как к начальному вводу информации в блоки 3-8 из распределителя 1 по обмоткам записи, включенным в цепи выходов распределителя, так и к передаче информации из регистров 3 и 4 в дешифратор адреса операнда 5 при считывании регистров 3 и 4 ло цепям 15 —. 16 и 17

1 8. При этом отпадает необходимость двоичного кодирования, а при вводе информации в дешифраторы 5 и 6 - необходи » мость перевода каждого двоичного разряда в код "1 из 2". Кроме того в устройстве функции одного регистра адреса полностью возложены на дешифратор 5.

При одноадресной системе команд реги- стры адреса операнда 3 и 4 отсутствуют вовсе. Функции регистра кода операции возложены на дешифратор кода операции

6. Функции постоянного запоминающего устройства распределены между всеми бло-: ками 3-8 и выполняются системой их об- моток записи.

Сердечники всех блоков 3»»8 не являются специально введенными с целью ор-: ганизации на них постоянного запоминающего устройства, они являются неотъем- : лемой частью самих блоков.

Предмет изобретения .Устройство для управления процессором, l

:содержащее распределитель, регистры адре са операнда, дешифратор адреса операнда,, входы которого подключены к соответствующим выходам регистров адреса операнда регистры адреса команды, выходы ко торых соединены с соответствующими входами распределителя, и дешифратор кода операции, отличaþøееся тем, что, с целью упрощения устройства и повышения его экономичности, в нем каждый выход распределителя подключен к соответ ствующим входам записи дешифратора адреса операнда, регистров адреса операнда, дешифратора кода операции и регистров адреса команды.

478307 юг. 2

Заказ g ßô Изд. 34 ЯЯ Тираж

Подписное

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24

Составитель

Л.геренов

Редактор Е.ГончаР Техред д.Казачков Корректор jl. ðàõíèíà