Статистический анализатор

Иллюстрации

Показать всеРеферат

Союз Соватских

Социалистимеских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 478;И7 (61) Зависимое от авт. свидетельства (22) Заявлено 25. 10.73 (21) 1966543/18-24 (51) М. Кл.

С- 06$ 15/36 с присоединением заявки №Я (32)Приоритет

Государственный комитет

Совета Министров СССР по делам изобретений и открытий

Опубликовано 25.07.75. Бюллетень № 2

Дата опубликования описания О - О8.7 (53) УДК 681.332:519, .2 (088.8) (72) Авторы изобретения

Н. И. 1 рибок, P. — À. В. Обуханич и С. С. Обозовский (71) Заявитель (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

Изобретение относится к области специализированных средств цифровой вычислительной техники, предназначенных для анапиза случайных процессов, т. е. для нахождения математического ожидания, дисперсии, среднеквадратического отклонения.

Известны устройства для вычисленияхарактеристик случаных процессов, выборки которых представлены в число-импульсных кодах. 10

Известное устройство содержит накапливающий сумматор, два двоичных счетчика, первую и вторую группы вентилей, счетчик выборок, схемы ИЛИ, два делителя частоты импульсов, генератор задержки, клапа- и ны и триггеры.

Однако в известном устройстве имеет место низкая частота следования импульсов унитарного кода вследствие использования генератора задержки, оценка средне- 20 квадратического отклонения пропорциональна корню квадратному из объема выборки, кроме того в нем невозможно получитьсреднее значение исследуемых сигналов.

Цель изобретения — повысить быстро- 25 действие и расширить функциональные возможности устройства.

Это достигается тем, что анализатор содержит второй накапливающий сумматор, соединенный с первой группой входов схемы сравнения кодов, входы второго накапливающего сумматора подключены к выходам второй группы вентилей, вторая группавходов схемы сравнения кодов соединена с вь.:-ходами первого накапливающего сумматора, подключенного к третьему триггеру, второй вход которого соединен с выходом первого клапана, а выход подключен к первому счетчику и к третьему клапану, выход второй схемы И через второй делитель частоты соединен с одним из входов второго накапливающего сумматора, выход схемы сравнения кодов подключен к одному из входов первой схемы И, выход которой соединен со схемой ИЛИ.

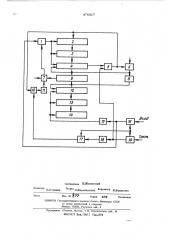

На чертеже показана блок-схема анализатора.

Устройство содержит схему ИЛИ 1,первый счетчик 2, первую группу вентилей 3, первый накапливающий сумматор 4, триг478317

rep 5, схемы И 6 и 7, схему сравнения кодов 8, делитель частоты импульсов 9, клапан 10, триггер 11, второй накапливающий сумматор 12, вторую группу вентилей

13, второй счетчик 14, второй делитель 5 частоты импульсов 15, клапан 16, триггер

17, счетчик выборки 18, клапан 19.

В исходном состоянии счетчики 2, 14, и 18, накапливающие сумматоры 4 и 12 и триггеры 5, 11 и 17 сброшены в состоя- 36 ние нуля. При этом клапаны 16 и 19 открыты по первому,входу, а клапан 10 закрыт по второму входу сигналом с выхода триггера 17.

Схема И 7 закрыта по третьему входу 15 сигналом с выхода триггера 11, а схема

И 6 закрыта по первому входу сигналом с выхода триггера 5.

Второй клапан 19 соединен с шиной

"такт", а выход подключен ко входу счет- 20 чика выборки 18 и ко входу установки в состояние l" триггера 5. Выход счетчика выборки 18 связан с входом установки в состояние "1" триггера 17, один из выходов которого подключен к первым входам 25 клапанов 16, 19, а второй выход — ко второму клапану 10, первый вход которого соединен со входом установки в нуль счет чика 2 и с выходом триггера 5. Выход клапана 10 связан со входом установки в 30 состояние 1 триггера 11, выход которого соединен со входом схемы И 7. Первый вход схемы И 7 подключен к источнику постоянной частоты, второй вход — к выходу схемы сравнения кодов 8, а выход через схему ИЛИ 1 связан со входом счетчика

2, с импульсным входом первой группы вентилей 3 и с суммирующим первым входом накапливающего сумматора 4. Информационные выходы счетчика 2 через груп- 4О пы вентилей 3 соединены со вХодами сумматора 4 таким образом, что выход первого разряда счетчика 2 подключен ко входу второго разряда сумматора, выход второго разряда счетчика — ко входу третьего 45 разряда и т. д. Благодаря этому при поступлении на импульсные входы импульса в сумматор 4 заносится удвоенное содержимое счетчика 2. Информационные выходы сумматора 4 подключены ко входам схемы 5О сравнения кодов 8, другие входы которой связаны с информационными выходами накапливающего сумматора 12. Вход установки в нуль триггера 5 связан с выходом сумматора 4, а выход подключен к первому входу схемы И 6, второй вход которой соединен с источником постоянной частоты, а выход подключен к второму суммирующему входу сумматора 4 и ко входу делителя частоты на 9, выход которого связан с первым вычитающим входом сумматора 12. Второй вход клапана 16 подключен ко входу устройства, а выход соединен с первым входом схемы ИЛИ 1, а через делитель 15 íà Q-c суммирующим входом счетчика 14., с импульсным входом второй группы вентилей 13 и со вторым вычитающим входом сумматора 12; Потенциальные входы группы вентилей 13 соеди- . нены с инверсными выходами триггеров счетчика 14, причем выход первого разряда счетчика 14 соединен со входом второго разряда накапливающего сумматора 12, выход второго разряда счетчика — со входом третьего и т. д.

Счетчик 2, группа вентилей .3, и нжапливающий сумматор 4 образуют квадратор, код в сумматоре которого равен квадрату числа импульсов, которые поступают на вход счетчика 2. Счетчик 14, группа вентилей 13 и сумматор 12 образуют квадратор, код чисел в сумматоре 12 которого равен дополнительному коду квадрата числа имцульсфа, которые поступают на вход счетчика 14. Для этого импульс с выхода делителя частоты 15 сначала записывается в счетчик 14 и сумматор 12, а потом поступает на вентили 13. С приходом первой выборки числа Х в сумматоре 12 зафиксирует1

tL (Х1) ся код яясде 2 — — где 11 -раз.

И рядность сумматора. Импульсы с выхода клапана 16 поступают через схему ИЛИ 1 на вход счетчика 2, группы вентилей 3 и накапливающего сумматора 4. При окончании занесения числа Х в сумматоре 4 зафиксирован код числа Х2. Импульс,.окон1 чания прохождения выборок "такт" перебрасывает триггер 5 в единичное состояние, который по первому входу открывает . схему И 6. При этом импульсы с ее выхсм да поступают на суммирующий вход накапливающего сумматора 4 и на делитель частоты на g9, импульсы с выхода которого поступают на вычитаюший вход сумматора 12. При поступлении на вход накапливающего сумматора 4 2 — Х2 импульсов

1 перепад на его выходе возвращает триггер

5 в исходное состояние, закрывая тем самым схему И 6 по первому входу и сбрасывая счетчик 2 в состояние нуля. К этому моменту в сумматоре 12 зафиксирован код числа

У =2 () + " = ((1

Х иХХ Х 2 к

При поступлении последующих значений выборок числа Х работа устройства происходит аналогично. После поступления N вы-.

478317 е борок значений числа Х в счетчике 14 зафиксирован код числа среднего арифметического, а в сумматоре 12 - дисперсии.

Я -й импульс такта приводит к переполнению счетчика выборки 18. При этом пе- ð репад на его выходе опрокидывает триггер

17 -в единичное состояние, что приводит к закрытию клапанов 16 и 19, по первым входам и к открытию клапана IO по втоь рому входу. При накоплении числа 2 -Х2 15

М с-сумматора 4 триггер 5 возвращается в нулевое .состояние. Перепад на его выходе сбрасывает счетчик 2 в нулевое состояние и проходит через клапан 10, опрокидывая триггер 11 в единичное состояние, 20 открывая тем самым схему И 7 по третьему входу. Схема сравнения кодов выдает разрешающий сигнал на второй вход, когда код числа в нака ливающем сумматоре

4 меньше или равен коду числа в накапливающем сумматоре 12. Это значит, что при окончании выборки схема И 7 по второму входу будет открыта, если значение дисперсии в накапливающем сумматоре 12 не равно нулю.

Импульсы с постоянной частотой поступают с выхода схемы И 7 через схему

ИЛИ 1 на вход счетчика 2, группы вентилей 3 и на первый вход накапливающего сумматора 4. В момент, когда код числа в сумматоре 4 будет равен или большекода числа в накапливающем сумматоре 12, сигнал с выхода схемы сравнения кодов 8 закроет схему И 7 по второму входу. При 0 этом в счетчике 12 будет зафиксирован код среднеквадратичного отклонения

6„=

45 с округлением в большую сторону.

В измерительно-вычислительных комплексах не так важно быстродействие обработки выборки объема N а более важно

1 50 расширение динамического диапазона обработки частоты следования импульсов унитарного кода. В предлагаемом устройстве эта частота ограничивается лишь быстродействием квадратора, который состоит

55 из счетчика 2, вентилей 3 и накапливающего сумматора 4.

Функциональные возможности ус ройства ° расширены за счет получения двоичного кода среднего значения в счетчике 14, дисперсии в накапливающем сумматоре 12 и среднего квадратичного отклонения всчетчике 2. При этом значение среднего значения и среднего квадратичного отклонения могут быть сняты в унитарном коде соответственно с выхода делителя частоты 15 и с выхода схемы И 7.

Предмет изобретения

Статистический анализатор, содержащий делитель и частоты, счетчики, информационные выходы которых подключены соответственно к первой и второй группе вентилей, первая группа вентилей соединена со входами накапливающего сумматора, первый и второй клапаны, информационные входы которых подключены соответственно к источнику обрабатываемого сигнала и к источнику тактовых импульсов, управляющие входы клапанов подключены к выходу первого триггера, вход которого соединен через счетчик выборки с выходом первого клапана, выход второго клапана подключен к первому делителю частоты, третий клапан, подключенный входом .к первому триггеру, а выходом — ко второму триггеру, схему

ИЛИ, подключенную одним входом к выходу второго клапана, первую и вторую схему И, первые входы которых соединены с генератором импульсов, а вторые соответственно подключены ко второму и третьему триггерам, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей анализатора, он содержит схему сравнения и дополнительный накапливающий сумматор, соединенный с первой группой входов схемы сравнения, входы дополнительного накапливающего сумматора подключены к выходам второй группы вентилей, вторая группа входов схемы сравнения соединена с выходами накапливающего сумматора, подключенного к третьему триггеру, второй вход которого соединен с выходом первого клапана, а выход подключен к первому счетчику и к третьему клапану, выход второй схемы

И через второй делитель частоты соединен с одним из входов дополнительного накапливающего сумматора, выход схемы сравнения подключен к одному из входов первой схемы И, выход которой соединен со схемой ИЛИ.

478317

Составитель В жовинснии

Техред H.Kàðàíäàøîâà Корректор В.Брыксина

Редактор

О.Стенина

Изд. М Тираж ЯЩ Подписное

Заказ

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24

ФКМП Зак.15011 Тир.679

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4