Устройство программного управления тернарного цифрового дифференциального анализатора

Иллюстрации

Показать всеРеферат

О П И С А Н И E (11) 47Ю32

ИЗОБРЕТЕНИЯ

Союз Советских

Свециалмстимесиих

Рес убл

К АВТОРСКОМУ СВИДЕТВЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 27.10.72 (21) 1846816/18-24 с присоединением заявки №(23) Приоритет(51) М. Кл.

G 06 1/02

Гевудврствеввав кемвтет

6ееете Меиевтрее ССИ ее девам «еебретеивк и еткрмтий

Опубликовано25.07.75. Бюллетень № 2 (Я) УАК 681 14 (088. 8) Дата опубликования описания 05.08.75

В. 3. Ляхович, В. ll. Баранов, Н. К. Ференец, Э. Л. Онишенко и

М. М. Сухомлинов (72) Авторы изобретения институт автоматики (71) Заявитель (54) УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ

ТЕРНАРНОГО БИФРОВОГО ДИФФЕРЕНБИАЛЬНОГО

АНАЛИЗАТОРА

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых интегрируюших машин.

Известны устройства программного управления тернарных цифровых дифференциальных анализаторов, содержащие блок па мяти, регистр, элемент "ИЛИ, выход которого соединен со входом регистра, элемент "НЕ", вход которого подключен к 10 первому выходу блока памяти, первый элемент "И", два входа которого подключены соответственно к выходам регистра и элемента HE", а выход соединен с первым входом элемента "ИЛИ", второй и у третий элементы "И", первые входы которых подключены к первому выходу блока памяти, вторые входы - к первому и второму входам устройства, выходы соединены со вторым и третьим входами элемента 20

"ИЛИ, а третий вход второго элемента

"И" подкшочен к третьему входу устройства, четвертый, пятый, шестой и седьмой . элементы "И", выходы которых соединены с выходами устройства, первые входы под- 26 ключены к выходу элемента "ИЛИ", вторые входы четвертого и пятого элементов И" подключены ко второму выходу блока памяти, вторые входы шестого и седьмого элементов "И" подключены к третьему выходу блока памяти, а третьи входы четвертого и шестого элементов "И подклю» чены к третьему входу устройства.

Белью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство содержит элемент задержки, вход которого подключен к третьему входу устройства, а выход соединен с третьими входами третьего, пятого и седьмого элег ментов "И .

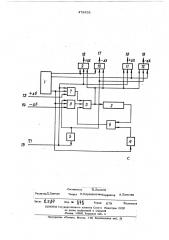

На чертеже изображено предлагаемое устройство.

Оно содержит блок памяти 1, регистр

2, элемент "ИЛИ» 3, элемент ".НЕ 4,,элемент задержки S, элементы "И 6-12, входы устройства 13-15 и выходы устройства 16-19.

Устройство работает следуюшим образом.

478332

Предмет изобретения

Устройство программного управления, З0 тернарного цифрового дифференциального анализатора, содержашее блок памяти, ре3

В устройстве для .хранения лоложитель- ных и отрицательных приращений исполу обуется не два регистра, а один. В блоке памяти 1 хранятся адреса записываемых и считываемых приращений. Запись и счи- б тывание положительных приращений осуществляется основным тактовым импульсом, поступающим на вход устройства 15. е

Запись и считывание отрицательных при-ращений выполняется по сдвинутому так- )0 товому импульсу с выхода элемента задержки 5.

Элементы И" 9 и 10 предназначены для считывания положительных и отрица. тельных приращений независимой перемен- }5 ной, а элементы "И" 11 и 12 — приращений подынтегральной функции.

Элементы "И" 7 и 8 служат для записи в регистр 2 положительных и отрицательных приращений, поступающих на входы 20 устройства 13 и 14. При записи нового приращения запрещается перезапись старого приращения. Этот запрет осуществляется подачей сигнала на элемент "HE

4 и тем самым запрещается сигнал на 25 выходе элемента "И» 6. гистр, элемент "ИЛИ, выход которого соединен со входом регистра, элемент

"HE", вход которого подключен к первому выходу блока памяти, первый элемент "И, два входа которого подключены соотвеч» ственно к выходам регистра и элемента

»HE", а выход соединен с первым входом элемента "ИЛИ", второй и третий элементы»И", первые входы которых подключены к первому выходу блока памяти, вторые г . входы — к первому и второму входам устройства, выходы соединены со вторым и третьим входами элемента "ИЛИ", а третий вход второго элемента "И"- подключен к третьему входу устройства, четвер.тый, пятый, шестой и седьмой элементы

"И", выходы которых соединены с выходами устройства, первые входы подключены к выходу элемента ИЛИ", вторые входы четвертого и пятого элементов И подключены ко второму выходу блока па мяти, вторые входы шестого и седьмого элементов "И" подключены к третьему выходу блока. памяти, а третьи входы четвертого и шестого элементов»И" подключены к третьему входу устройства, отличаюшеесятем,что, с целью упрощения„устройство содержит элемент задержки, вход которого подклкк; чен к третьему входу устройства, а выход соединен с третьими входами третьего, пятого и седьмого элементов»И".

478332

7о

Составитеяь B.Ëûøêîâ

Техред И.Карандашова корректор А.0зесова

; РедакторД.Пинчук

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24

Зазаз аз Sg / Изд. дд Щ таран о зоа Иодпноное